# ESP32

# **Hardware Design Guidelines**

## **Table of contents**

| 1 a | ible of | contents   |                                                                                       | 1  |  |  |  |  |

|-----|---------|------------|---------------------------------------------------------------------------------------|----|--|--|--|--|

| 1   | Late    | st Version | of This Document                                                                      | 3  |  |  |  |  |

|     | 1.1     |            | his Document                                                                          | 3  |  |  |  |  |

|     |         |            | Introduction                                                                          | 3  |  |  |  |  |

|     |         | 1.1.2      | Latest Version of This Document                                                       | 3  |  |  |  |  |

|     | 1.2     |            | Overview                                                                              | 3  |  |  |  |  |

|     | 1.3     |            | ic Checklist                                                                          | 4  |  |  |  |  |

|     |         |            | Overview                                                                              | 4  |  |  |  |  |

|     |         |            | Power Supply                                                                          | 6  |  |  |  |  |

|     |         |            | Chip Power-up and Reset Timing                                                        | 8  |  |  |  |  |

|     |         |            | Flash and PSRAM                                                                       | 9  |  |  |  |  |

|     |         |            | Clock Source                                                                          | 10 |  |  |  |  |

|     |         | 1.3.6      | RF                                                                                    | 12 |  |  |  |  |

|     |         |            | UART                                                                                  | 12 |  |  |  |  |

|     |         | 1.3.8      | SPI                                                                                   | 13 |  |  |  |  |

|     |         | 1.3.9      | Strapping Pins                                                                        | 13 |  |  |  |  |

|     |         |            | GPIO                                                                                  | 14 |  |  |  |  |

|     |         |            | ADC                                                                                   | 16 |  |  |  |  |

|     |         |            | External Capacitor                                                                    | 16 |  |  |  |  |

|     |         |            | SDIO                                                                                  | 16 |  |  |  |  |

|     |         | 1.3.14     | Touch Sensor                                                                          | 17 |  |  |  |  |

|     |         |            | Ethernet MAC                                                                          | 17 |  |  |  |  |

|     | 1.4     | PCB Lay    | out Design                                                                            | 18 |  |  |  |  |

|     |         |            | General Principles of PCB Layout for the Chip                                         | 18 |  |  |  |  |

|     |         | 1.4.2      | Power Supply                                                                          | 18 |  |  |  |  |

|     |         |            | Crystal                                                                               | 20 |  |  |  |  |

|     |         |            | RF                                                                                    | 21 |  |  |  |  |

|     |         | 1.4.5      | Flash and PSRAM                                                                       | 23 |  |  |  |  |

|     |         | 1.4.6      | External RC                                                                           | 25 |  |  |  |  |

|     |         | 1.4.7      | UART                                                                                  | 25 |  |  |  |  |

|     |         |            | General Principles of PCB Layout for Modules (Positioning a Module on a Base Board) . | 25 |  |  |  |  |

|     |         | 1.4.9      | SDIO                                                                                  | 25 |  |  |  |  |

|     |         | 1.4.10     | Touch Sensor                                                                          | 27 |  |  |  |  |

|     |         | 1.4.11     | Typical Layout Problems and Solutions                                                 | 29 |  |  |  |  |

|     | 1.5     | Hardward   | e Development                                                                         | 29 |  |  |  |  |

|     |         |            | ESP32 Modules                                                                         | 30 |  |  |  |  |

|     |         |            | ESP32 Development Boards                                                              | 30 |  |  |  |  |

|     |         |            | Download Guidelines                                                                   | 30 |  |  |  |  |

|     | 1.6     |            | Documentation and Resources                                                           | 30 |  |  |  |  |

|     | 1.7     | Glossary   |                                                                                       | 31 |  |  |  |  |

|     | 1.8     |            | History                                                                               | 31 |  |  |  |  |

|     | 1.9     |            |                                                                                       |    |  |  |  |  |

This document provides guidelines for the ESP32 SoC.

## **Chapter 1**

## **Latest Version of This Document**

Check the link to make sure that you use the latest version of this document: https://docs.espressif.com/projects/esp-hardware-design-guidelines/en/latest/esp32/index.html

## 1.1 About This Document

#### 1.1.1 Introduction

The hardware design guidelines advise on how to integrate ESP32 into a product. These guidelines will help to achieve optimal performance of your product, ensuring technical accuracy and adherence to Espressif's standards. The guidelines are intended for hardware and application engineers.

The document assumes that you possess a certain level of familiarity with the ESP32 SoC. In case you lack prior knowledge, we recommend utilizing this document in conjunction with the ESP32 Series Datasheet.

## 1.1.2 Latest Version of This Document

Check the link to make sure that you use the latest version of this document: https://docs.espressif.com/projects/esp-hardware-design-guidelines/en/latest/esp32/index.html

## 1.2 Product Overview

ESP32 is a system on a chip that integrates the following features:

- Wi-Fi (2.4 GHz band)

- Bluetooth®

- Dual high-performance Xtensa® 32-bit LX6 CPU cores

- Ultra Low Power coprocessor

- Multiple peripherals

Powered by 40 nm technology, ESP32 provides a robust, highly-integrated platform, which helps meet the continuous demands for efficient power usage, compact design, security, high performance, and reliability. Typical application scenarios for ESP32 include:

· Smart Home

- Industrial Automation

- · Health Care

- Consumer Electronics

- Smart Agriculture

- · POS Machines

- · Service Robot

- · Audio Devices

- Generic Low-power IoT Sensor Hubs

- Generic Low-power IoT Data Loggers

- · Cameras for Video Streaming

- Speech Recognition

- Image Recognition

- SDIO Wi-Fi + Bluetooth Networking Card

- · Touch and Proximity Sensing

For more information about ESP32, please refer to ESP32 Series Datasheet.

**Note:** Unless otherwise specified, "ESP32" used in this document refers to the series of chips, instead of a specific chip variant.

### 1.3 Schematic Checklist

#### 1.3.1 Overview

The integrated circuitry of ESP32 requires only 20 electrical components (resistors, capacitors, and inductors) and a crystal, as well as an SPI flash. The high integration of ESP32 allows for simple peripheral circuit design. This chapter details the schematic design of ESP32.

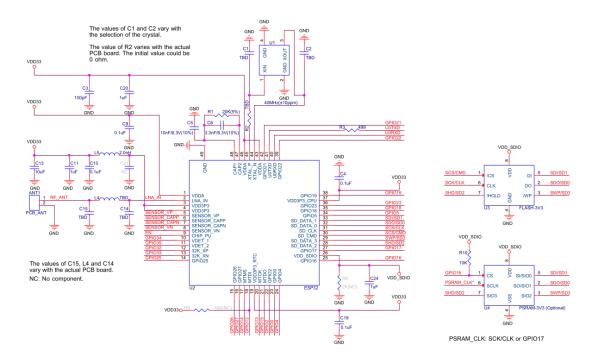

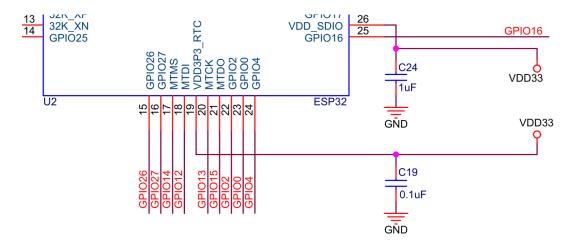

The following figure shows a reference schematic design of ESP32. It can be used as the basis of your schematic design.

Note that Figure *ESP32 Reference Schematic* shows the connection for quad 3.3 V external flash/PSRAM. PSRAM's SCLK and flash can share the clock from SD\_CLK or GPIO17.

- $\bullet\,$  In cases where quad 1.8 V external flash/PSRAM is used, R9 should be populated.

- In cases where ESP32-D0WDR2-V3 with in-package quad 3.3 V PSRAM is used, the external flash can be connected as Figure *ESP32 Reference Schematic* shows.

- In cases where ESP32-U4WDH with in-package quad 3.3 V flash is used, the in-package flash is connected as Figure ESP32 Schematic for Quad 3.3 V In-Package Flash shows.

Any basic ESP32 circuit design may be broken down into the following major building blocks:

- Power supply

- Chip power-up and reset timing

- Flash and PSRAM

- Clock source

- *RF*

- UART

- Strapping pins

- GPIO

- *ADC*

- External capacitor

- SDIO

Fig. 1: ESP32 Reference Schematic

Fig. 2: ESP32 Schematic for Quad 3.3 V In-Package Flash

Touch sensor

The rest of this chapter details the specifics of circuit design for each of these sections.

## 1.3.2 Power Supply

The general recommendations for power supply design are:

- When using a single power supply, the recommended power supply voltage is 3.3 V and the output current is no less than 500 mA.

- It is suggested to add an ESD protection diode at each power entrance.

The power scheme is shown in ESP32 Series Datasheet > Figure ESP32 Power Scheme.

More information about power supply pins can be found in ESP32 Series Datasheet > Section Power Supply.

#### **Digital Power Supply**

ESP32 has pin37 VDD3P3\_CPU as the digital power supply pin(s) working in a voltage range of 1.8 V ~ 3.6 V. It is recommended to add an extra 0.1  $\mu$ F decoupling capacitor close to the pin(s).

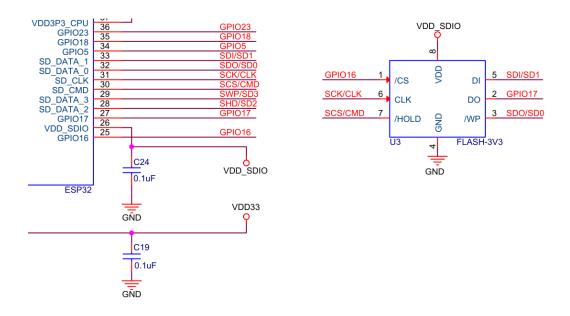

Pin VDD\_SDIO can serve as the power supply for the external device at either 1.8 V or 3.3 V (default).

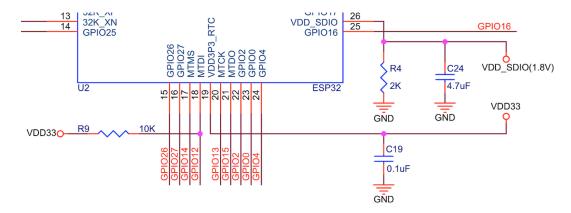

- When VDD\_SDIO operates at 1.8 V, it is powered by ESP32's internal LDO. The maximum current this LDO can offer is 40 mA, and the output voltage range is 1.65 V ~ 2.0 V. When the VDD\_SDIO outputs 1.8 V, it is recommended that users add a 2 k $\Omega$  ground resistor and a 4.7  $\mu$ F ground capacitor close to VDD\_SDIO. See Figure ESP32 Schematic for 1.8 V VDD\_SDIO Power Supply Pin.

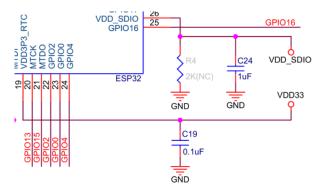

- When VDD\_SDIO operates at 3.3 V, it is driven directly by VDD3P3\_RTC through a 6 Ω resistor (internal to the chip), therefore, there will be some voltage drop from VDD3P3\_RTC. When the VDD\_SDIO outputs 3.3 V, it is recommended that users add a 1 μF filter capacitor close to VDD\_SDIO. See Figure ESP32 Schematic for 3.3 V VDD\_SDIO Power Supply Pin.

**Attention:** When using VDD\_SDIO as the power supply pin for in-package or off-package 3.3 V flash/PSRAM, the supply voltage should be 3.0 V or above, so as to meet the requirements of flash/PSRAM's working voltage.

Fig. 3: ESP32 Schematic for 1.8 V VDD\_SDIO Power Supply Pin

VDD\_SDIO can also be driven by an external power supply as shown in Figure ESP32 Schematic for VDD\_SDIO Pin Powered by External Supply.

#### **Analog Power Supply**

ESP32' s VDDA and VDD3P3 pins are the analog power supply pins, working at  $2.3 \text{ V} \sim 3.6 \text{ V}$ .

Fig. 4: ESP32 Schematic for 3.3 V VDD\_SDIO Power Supply Pin

Fig. 5: ESP32 Schematic for VDD\_SDIO Pin Powered by External Supply

For VDD3P3, when ESP32 is transmitting signals, there may be a sudden increase in the current draw, causing power rail collapse. Therefore, it is highly recommended to add a  $10~\mu F$  capacitor to the power rail, which can work in conjunction with the  $1~\mu F$  capacitor(s).

Add a LC circuit on the VDD3P3 power rail to suppress high-frequency harmonics. The inductor's rated current is preferably 500 mA and above.

#### **RTC Power Supply**

ESP32's VDD3P3\_RTC pin is the RTC and analog power pin. It is recommended to place a  $0.1~\mu F$  decoupling capacitor near this power pin in the circuit.

Note that this power supply cannot be used as a single backup power supply.

The schematic for the RTC power supply pin is shown in Figure ESP32 Schematic for RTC Power Supply Pin.

Fig. 6: ESP32 Schematic for RTC Power Supply Pin

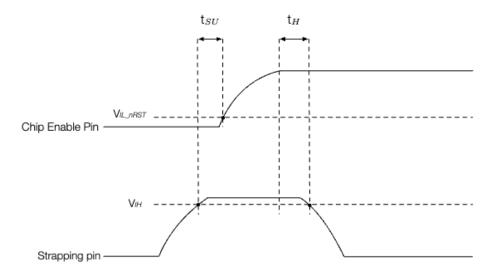

### 1.3.3 Chip Power-up and Reset Timing

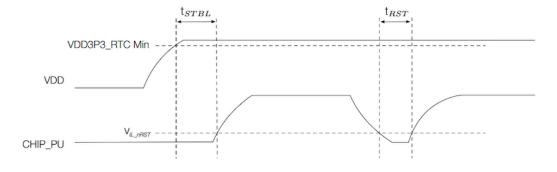

ESP32' s CHIP\_PU pin can enable the chip when it is high and reset the chip when it is low.

When ESP32 uses a 3.3 V system power supply, the power rails need some time to stabilize before CHIP\_PU is pulled up and the chip is enabled. Therefore, CHIP\_PU needs to be asserted high after the 3.3 V rails have been brought up.

To reset the chip, keep the reset voltage  $V_{IL\_nRST}$  in the range of (-0.3 ~ 0.25 × VDD) V. To avoid reboots caused by external interferences, make the CHIP\_PU trace as short as possible.

Figure ESP32 Power-up and Reset Timing shows the power-up and reset timing of ESP32.

Fig. 7: ESP32 Power-up and Reset Timing

Table Description of Timing Parameters for Power-up and Reset provides the specific timing requirements.

Table 1: Description of Timing Parameters for Power-up and Reset

| Parameter         | Description                                                                   | Minimum (μs) |  |  |

|-------------------|-------------------------------------------------------------------------------|--------------|--|--|

| t <sub>STBL</sub> | Time reserved for the power rails to stabilize before the CHIP_PU             |              |  |  |

|                   | pin is pulled high to activate the chip                                       |              |  |  |

| t <sub>RST</sub>  | $t_{RST}$ Time reserved for CHIP_PU to stay below $V_{IL\_nRST}$ to reset the |              |  |  |

|                   | chip                                                                          |              |  |  |

#### **Attention:**

- CHIP\_PU must not be left floating.

- To ensure the correct power-up and reset timing, it is advised to add an RC delay circuit at the CHIP\_PU pin. The recommended setting for the RC delay circuit is usually  $R = 10 \, k\Omega$  and  $C = 1 \, \mu F$ . However, specific parameters should be adjusted based on the characteristics of the actual power supply and the power-up and reset timing of the chip.

- If the user application has one of the following scenarios:

- Slow power rise or fall, such as during battery charging.

- Frequent power on/off operations.

- Unstable power supply, such as in photovoltaic power generation.

Then, the RC circuit itself may not meet the timing requirements, resulting in the chip being unable to boot correctly. In this case, additional designs need to be added, such as:

- Adding an external reset chip or a watchdog chip, typically with a threshold of around 3.0 V.

- Implementing reset functionality through a button or the main controller.

#### 1.3.4 Flash and PSRAM

ESP32 requires in-package or off-package flash to store application firmware and data. In-package PSRAM or off-package PSRAM is optional.

#### **In-Package Flash and PSRAM**

The tables list the pin-to-pin mapping between the chip and in-package flash/PSRAM. Please note that the following chip pins can connect at most one flash and one PSRAM. That is to say, when there is only flash in the package, the pin occupied by flash can only connect PSRAM and cannot be used for other functions; when there is only PSRAM, the pin occupied by PSRAM can only connect flash; when there are both flash and PSRAM, the pin occupied cannot connect any more flash or PSRAM.

Table 2: Pin-to-Pin Mapping Between Chip and In-Package Flash

| ESP32-U4WDH | In-Package Flash (4 MB) |

|-------------|-------------------------|

| SD_DATA_1   | IO0/DI                  |

| GPIO17      | IO1/DO                  |

| SD_DATA_0   | IO2/WP#                 |

| SD_CMD      | IO3/HOLD#               |

| SD_CLK      | CLK                     |

| GPIO16      | CS#                     |

| GND         | VSS                     |

| VDD_SDIO    | VDD                     |

| 11 6            |                         |

|-----------------|-------------------------|

| ESP32-D0WDR2-V3 | In-Package PSRAM (2 MB) |

| SD_DATA_1       | SIO0/SI                 |

| SD_DATA_0       | SIO1/SO                 |

| SD_DATA_3       | SIO2                    |

| SD_DATA_2       | SIO3                    |

| SD_CLK          | SCLK                    |

| GPIO16          | CE#                     |

| GND             | VSS                     |

| VDD SDIO        | VDD                     |

Table 3: Pin-to-Pin Mapping Between Chip and In-Package PSRAM

#### **Off-Package Flash and PSRAM**

To reduce the risk of software compatibility issues, please use flash and PSRAM models officially validated by Espressif. For detailed model selection, consult the sales or technical support team. If VDD\_SDIO is used to supply power, make sure to select the appropriate off-package flash and RAM according to the power voltage on VDD\_SDIO (1.8 V/3.3 V). It is recommended to add zero-ohm resistor footprints in series on the SPI communication lines. These footprints provide flexibility for future adjustments, such as tuning drive strength, mitigating RF interference, correcting signal timing, and reducing noise, if needed.

#### 1.3.5 Clock Source

ESP32 supports two external clock sources:

- External crystal clock source (Compulsory)

- RTC clock source (Optional)

#### **External Crystal Clock Source (Compulsory)**

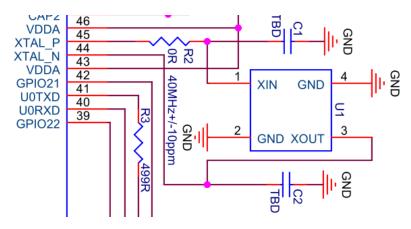

The ESP32 firmware only supports 40 MHz crystal.

The circuit for the crystal is shown in Figure ESP32 Schematic for External Crystal. Note that the accuracy of the selected crystal should be within  $\pm 10$  ppm.

Fig. 8: ESP32 Schematic for External Crystal

Please add a series inductor on the XTAL\_P clock trace. Initially, it is suggested to use an inductor of 24 nH to reduce the impact of high-frequency crystal harmonics on RF performance, and the value should be adjusted after an overall test.

The initial values of external capacitors C1 and C2 can be determined according to the formula:

$$C_L = \frac{C1 \times C2}{C1 + C2} + C_{stray}$$

where the value of  $C_L$  (load capacitance) can be found in the crystal's datasheet, and the value of  $C_{\text{stray}}$  refers to the PCB's stray capacitance. The values of C1 and C2 need to be further adjusted after an overall test as below:

- 1. Select TX tone mode using the Certification and Test Tool.

- 2. Observe the 2.4 GHz signal with a radio communication analyzer or a spectrum analyzer and demodulate it to obtain the actual frequency offset.

- 3. Adjust the frequency offset to be within ±10 ppm (recommended) by adjusting the external load capacitance.

- When the center frequency offset is positive, it means that the equivalent load capacitance is small, and the external load capacitance needs to be increased.

- When the center frequency offset is negative, it means the equivalent load capacitance is large, and the external load capacitance needs to be reduced.

- External load capacitance at the two sides are usually equal, but in special cases, they may have slightly different values.

#### Note:

- Defects in the manufacturing of crystal (for example, large frequency deviation of more than ±10 ppm, unstable performance within the operating temperature range, etc) may lead to the malfunction of ESP32, resulting in a decrease of the RF performance.

- It is recommended that the amplitude of the crystal is greater than 500 mV.

- When Wi-Fi or Bluetooth connection fails, after ruling out software problems, you may follow the steps mentioned above to ensure that the frequency offset meets the requirements by adjusting capacitors at the two sides of the crystal.

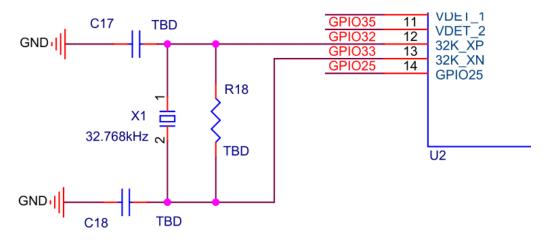

#### **RTC Clock Source (Optional)**

ESP32 supports an external 32.768 kHz crystal to act as the RTC clock. The external RTC clock source enhances timing accuracy and consequently decreases average power consumption, without impacting functionality.

Figure ESP32 Schematic for 32.768 kHz Crystal shows the schematic for the external 32.768 kHz crystal.

Fig. 9: ESP32 Schematic for 32.768 kHz Crystal

Please note the requirements for the 32.768 kHz crystal:

- Equivalent series resistance (ESR)  $\leq 70 \text{ k}\Omega$ .

- Load capacitance at both ends should be configured according to the crystal's specification.

The parallel resistor R is used for biasing the crystal circuit (5 M $\Omega$  < R  $\leq$  10 M $\Omega$ ).

For chip revisions v1.0 or v1.1, it is not recommended to use a 32.768 kHz crystal. For chip revisions v3.0 or higher, a 32.768 kHz crystal can be used, but the parallel resistor R must be installed.

If the RTC clock source is not required, then the pins for the 32.768 kHz crystal can be used as GPIOs.

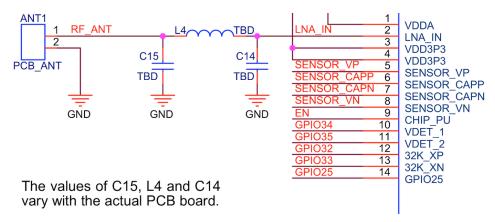

#### 1.3.6 RF

#### **RF** Circuit

ESP32' s RF circuit is mainly composed of three parts, the RF traces on the PCB board, the chip matching circuit, the antenna and the antenna matching circuit. Each part should meet the following requirements:

- For the RF traces on the PCB board,  $50 \Omega$  impedance control is required.

- For the chip matching circuit, it must be placed close to the chip. A CLC structure is preferred.

- The CLC structure is mainly used to adjust the impedance point and suppress harmonics, and a set of LC can be added if space permits.

- The RF matching circuit is shown in Figure ESP32 Schematic for RF Matching.

- For the antenna and the antenna matching circuit, to ensure radiation performance, the antenna's characteristic impedance must be around 50  $\Omega$ . Adding a CLC matching circuit near the antenna is recommended to adjust the antenna. However, if the available space is limited and the antenna impedance point can be guaranteed to be 50  $\Omega$  by simulation, then there is no need to add a matching circuit near the antenna.

Fig. 10: ESP32 Schematic for RF Matching

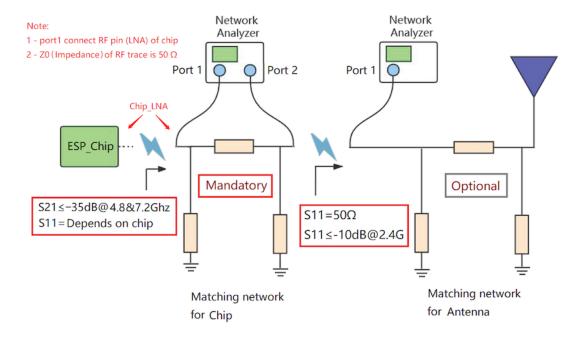

#### **RF** Tuning

The RF matching parameters vary with the board, so the ones used in Espressif modules could not be applied directly. Follow the instructions below to do RF tuning.

Figure ESP32 RF Tuning Diagram shows the general process of RF tuning.

The initial value of the parameters in the matching network can be  $0 \Omega$ . The recommended value of S11 is 25+j0. The recommended central frequency is 2442 MHz.

Note: If RF function is not required, then the RF pin can be left floating.

#### 1.3.7 UART

Usually, UART0 is used as the serial port for download and log printing. For instructions on download over UART0, please refer to Section *Download Guidelines*. It is recommended to connect a 499  $\Omega$  series resistor to the U0TXD

Fig. 11: ESP32 RF Tuning Diagram

line to suppress harmonics.

If possible, use other UART interfaces as serial ports for communication. For these interfaces, it is suggested to add a series resistor to the TX line to suppress harmonics.

When using the AT firmware, please note that the UART GPIO is already configured (refer to Hardware Connection). It is recommended to use the default configuration.

#### 1.3.8 SPI

When using the SPI function, to improve EMC performance, add a series resistor (or ferrite bead) and a capacitor to ground on the SPI\_CLK trace. If space allows, it is recommended to also add a series resistor and capacitor to ground on other SPI traces. Ensure that the RC/LC components are placed close to the pins of the chip or module.

### 1.3.9 Strapping Pins

At each startup or reset, a chip requires some initial configuration parameters, such as in which boot mode to load the chip, etc. These parameters are passed over via the strapping pins. After reset, the strapping pins work as normal function pins.

GPIO0, GPIO2, GPIO5, MTDI, and MTDO are strapping pins.

All the information about strapping pins is covered in ESP32 Series Datasheet > Chapter Boot Configurations.

In this document, we will mainly cover the strapping pins related to boot mode.

After chip reset is released, the combination of GPIO0 and GPIO2 controls the boot mode. See Table *Boot Mode Control*.

Boot Mode

GPIO0

GPIO2

Default Config

1

0

SPI Boot

1

Any value

Joint Download Boot<sup>1</sup>

0

0

Table 4: Boot Mode Control

Signals applied to the strapping pins should have specific *setup time* and *hold time*. For more information, see Figure *Setup and Hold Times for Strapping Pins* and Table *Description of Timing Parameters for Strapping Pins*.

Fig. 12: Setup and Hold Times for Strapping Pins

Table 5: Description of Timing Parameters for Strapping Pins

| Parameter      | Description                                                           | Minimum (ms) |

|----------------|-----------------------------------------------------------------------|--------------|

| $t_{ m SU}$    | Time reserved for the power rails to stabilize before the chip enable | 0            |

|                | pin (CHIP_PU) is pulled high to activate the chip.                    |              |

| t <sub>H</sub> | Time reserved for the chip to read the strapping pin values after     | 3            |

|                | CHIP_PU is already high and before these pins start operating as      |              |

|                | regular IO pins.                                                      |              |

#### **Attention:**

- It is recommended to place a pull-up resistor at the GPIO0 pin.

- Do not add high-value capacitors at GPIO0, or the chip may enter download mode.

## 1.3.10 GPIO

The pins of ESP32 can be configured via IO MUX or GPIO matrix. IO MUX provides the default pin configurations (see ESP32 Series Datasheet > Appendix ESP32 Consolidated Pin Overview), whereas the GPIO matrix is used to route signals from peripherals to GPIO pins. For more information about IO MUX and GPIO matrix, please refer to ESP32 Technical Reference Manual > Chapter IO MUX and GPIO Matrix.

Some peripheral signals have already been routed to certain GPIO pins, while some can be routed to any available GPIO pins. For details, please refer to ESP32 Series Datasheet > Section *Peripherals*.

When using GPIOs, please:

- Pay attention to the states of strapping pins during power-up.

- <sup>1</sup> Joint Download Boot mode supports the following download methods:

- · UART Download Boot

- SDIO Download Boot

- Pay attention to the default configurations of the GPIOs after reset. The default configurations can be found in the table below. It is recommended to add a pull-up or pull-down resistor to pins in the high-impedance state or enable the pull-up and pull-down during software initialization to avoid extra power consumption.

- Avoid using the pins already occupied by flash/PSRAM.

Table 6: IO MUX Pin Functions

| GPIO | Pin     | Func-              | Func-            | Func-  | Func-   | Func-               | Func-   | Reset  |

|------|---------|--------------------|------------------|--------|---------|---------------------|---------|--------|

|      | Name    | tion               | tion             | tion   | tion    | tion                | tion    | 110001 |

|      | 1100    | 0                  | 1                | 2      | 3       | 4                   | 5       |        |

| 0    | GPIO0   | GPIO0              | CLK_OU           |        | _       | _                   | EMAC_T  | X3 CLK |

| 1    | U0TXD   | U0TXD              | CLK_OU           |        | _       | _                   | EMAC_R  |        |

| 2    | GPIO2   | GPIO2              | HSPIWP           |        |         | TASOD DATA          |         | 2      |

| 3    | U0RXD   | U0RXD              | CLK_OU           |        | _       | _                   | _       | 3      |

| 4    | GPIO4   | GPIO4              |                  | GPIO4  | HS2_DA7 | TASD_DAT            | AEMAC_T | X2_ER  |

| 5    | GPIO5   | GPIO5              | VSPICS0          | GPIO5  | HS1_DA  |                     | EMAC_R  |        |

| 6    | SD_CLK  | SD_CLK             | SPI-             | GPIO6  | HS1_CLF | U1CTS               | _       | 3      |

|      |         |                    | CLK              |        |         |                     |         |        |

| 7    | SD_DATA | A <u>S</u> OD_DATA | A <b>®</b> PIQ   | GPIO7  | HS1_DA7 | Γ <b>A</b>          | _       | 3      |

| 8    | SD_DATA | ASD_DATA           | A SPID           | GPIO8  | HS1_DA7 | TAU2CTS             | _       | 3      |

| 9    | SD_DATA | ASD_DATA           | A <b>S</b> PIHD  | GPIO9  | HS1_DA7 | Γ <b>A</b> 21RXD    | _       | 3      |

| 10   | SD_DATA | ASD_DATA           | A <b>\$</b> PIWP | GPIO10 | HS1_DA7 | Γ <b>A</b> β1TXD    | _       | 3      |

| 11   | SD_CMD  | SD_CMD             | SPICS0           | GPIO11 | HS1_CM  | DU1RTS              | _       | 3      |

| 12   | MTDI    | MTDI               | HSPIQ            | GPIO12 | HS2_DA7 | TAS2D_DAT           | AÆMAC_T | XD3    |

| 13   | MTCK    | MTCK               | HSPID            | GPIO13 | HS2_DA7 | Γ <b>ΑS3</b> D_DAT. | AÆMAC_R | X2_ER  |

| 14   | MTMS    | MTMS               | HSPI-            | GPIO14 | HS2_CLF | SD_CLK              | EMAC_T  | X3D2   |

|      |         |                    | CLK              |        |         |                     |         |        |

| 15   | MTDO    | MTDO               | HSPICS0          | GPIO15 | HS2_CM  | DSD_CMD             | EMAC_R  | XD3    |

| 16   | GPIO16  | GPIO16             | _                | GPIO16 | HS1_DA7 | Γ <b>A</b> 42RXD    | EMAC_C  | LK_OUT |

| 17   | GPIO17  | GPIO17             | _                | GPIO17 | HS1_DA7 | Γ <b>Α5</b> 2TXD    | EMAC_C  | LK_180 |

| 18   | GPIO18  | GPIO18             | VSPI-            | GPIO18 | HS1_DA7 | Γ <b>Α</b> -7       | _       | 1      |

|      |         |                    | CLK              |        |         |                     |         |        |

| 19   | GPIO19  | GPIO19             | VSPIQ            | GPIO19 | U0CTS   | _                   | EMAC_T  | XD0    |

| 21   | GPIO21  | GPIO21             | VSPIHD           | GPIO21 | _       | _                   | EMAC_T  |        |

| 22   | GPIO22  | GPIO22             | VSPIWP           | GPIO22 | U0RTS   | _                   | EMAC_T  | XD1    |

| 23   | GPIO23  | GPIO23             | VSPID            | GPIO23 | HS1_STR | OBE                 | _       | 1      |

| 25   | GPIO25  | GPIO25             | _                | GPIO25 | _       | _                   | EMAC_R  | XD0    |

| 26   | GPIO26  | GPIO26             | _                | GPIO26 | _       | _                   | EMAC_R  |        |

| 27   | GPIO27  | GPIO27             | _                | GPIO27 | _       | _                   | EMAC_R  | XO_DV  |

| 32   | 32K_XP  | GPIO32             | _                | GPIO32 | _       | _                   | _       | 0      |

| 33   | 32K_XN  |                    | _                | GPIO33 | _       | _                   | _       | 0      |

| 34   | VDET_1  | GPIO34             | _                | GPIO34 | _       | _                   | _       | 0      |

| 35   | VDET_2  | GPIO35             | _                | GPIO35 | _       | _                   | _       | 0      |

| 36   | SEN-    | GPIO36             | _                | GPIO36 | _       | _                   | _       | 0      |

|      | SOR_VP  |                    |                  |        |         |                     |         |        |

| 37   | SEN-    | GPIO37             | _                | GPIO37 |         | _                   | _       | 0      |

|      | SOR_CA  |                    |                  |        |         |                     |         |        |

| 38   | SEN-    | GPIO38             | -                | GPIO38 |         | _                   | _       | 0      |

|      | SOR_CA  |                    |                  |        |         |                     |         |        |

| 39   | SEN-    | GPIO39             | -                | GPIO39 |         | _                   | _       | 0      |

|      | SOR_VN  |                    |                  |        |         |                     |         |        |

#### **Reset:**

- 0: IE=0 (input disabled)

- 1: IE=1 (input enabled)

- 2: IE=1, WPD=1 (input enabled, pull-down resistor)

- 3: IE=1, WPU=1 (input enabled, pull-up resistor)

#### 1.3.11 ADC

Please add a 0.1 µF filter capacitor between ESP pins and ground when using the ADC function to improve accuracy.

When RTC peripherals (SAR ADC1/SAR ADC2/AMP) is powered on, the inputs of GPIO36 (SENSOR\_VP) and GPIO39 (SENSOR\_VN) will be pulled down for approximately 80 ns. Therefore, it is recommended to use SENSOR\_VP and SENSOR\_VN as ADC pins.

If SENSOR\_VP and SENSOR\_VN are used as GPIOs in the design, while ADC is supported by other pins, then software should disregard the glitch. Optionally, make SENSOR\_VP and SENSOR\_VN active high pins.

ADC1 is recommended over ADC2 as the latter cannot be used when Wi-Fi function is enabled.

The calibrated ADC results after hardware calibration and software calibration are shown in the list below. For higher accuracy, you may implement your own calibration methods.

- When ATTEN=0 and the effective measurement range is 100 ~ 950 mV, the total error is ±23 mV.

- When ATTEN=1 and the effective measurement range is 100 ~ 1250 mV, the total error is ±30 mV.

- When ATTEN=2 and the effective measurement range is 150 ~ 1750 mV, the total error is ±40 mV.

- When ATTEN=3 and the effective measurement range is 150 ~ 2450 mV, the total error is ±60 mV.

### 1.3.12 External Capacitor

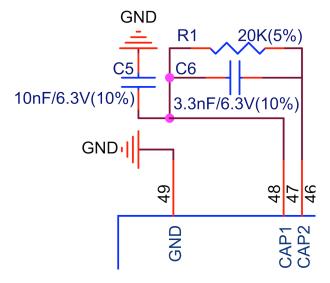

Figure ESP32 Schematic for External Capacitor shows the schematic of components connected to pin47 CAP2 and pin48 CAP1.

C5 (10 nF) that connects to CAP1 should be of 10% tolerance and is required for proper operation of ESP32.

RC circuit between CAP1 and CAP2 pins may be omitted under certain conditions. This circuit is used when entering Deep-sleep mode. During this process, to minimize power consumption, the voltage to power ESP32 internals is dropped from 1.1 V to around 0.7 V. The RC circuit is used to minimize the period of the voltage drop. If removed, this process will take longer and the power consumption in Deep-sleep will be higher. If particular application of ESP32 is not using Deep-sleep mode, or power consumption is less critical, then this circuit is not required.

Fig. 13: ESP32 Schematic for External Capacitor

### 1.3.13 SDIO

There are two sets of GPIOs (slot0 and slot1) that can be assigned to SDIO on ESP32, as shown in Table *SDIO Pin Configuration*. When ESP32 works as an SDIO host or slave, connect GPIOs in slot1 to signal lines.

|       | Tuble 7. 5516 Till Collinguitation |        |       |       |        |        |                               |

|-------|------------------------------------|--------|-------|-------|--------|--------|-------------------------------|

|       | CMD                                | CLK    | DAT0  | DAT1  | DAT2   | DAT3   | Note                          |

| Slot0 | GPIO11                             | GPIO6  | GPIO7 | GPIO8 | GPIO9  | GPIO10 | Used to connect flash by de-  |

|       |                                    |        |       |       |        |        | fault. Not recommended for    |

|       |                                    |        |       |       |        |        | other use.                    |

| Slot1 | GPIO15                             | GPIO14 | GPIO2 | GPIO4 | GPIO12 | GPIO13 | Multiplexed with JTAG, touch, |

|       |                                    |        |       |       |        |        | EMAC, and strapping func-     |

|       |                                    |        |       |       |        |        | tions.                        |

Table 7: SDIO Pin Configuration

When connecting GPIOs in slot1 to signal lines, please note:

- When ESP32 works as an SDIO host, it is recommended to add pull-up resistors on the used pins. Unused pins can be utilized for other purposes.

- When ESP32 works as an SDIO slave, add pull-up resistors on all pins, regardless of whether these pins are used for SDIO or not. Unused pins cannot be used for other purposes.

For more information on SDIO configuration, please refer to API References.

#### 1.3.14 Touch Sensor

When using the touch function, it is recommended to populate a series resistor at the chip side to reduce the coupling noise and interference on the line, and to strengthen the ESD protection. The recommended resistance is from 470  $\Omega$  to 2 k $\Omega$ , preferably 510  $\Omega$ . The specific value depends on the actual test results of the product.

#### 1.3.15 Ethernet MAC

ESP32 provides a media access control (MAC) interface that complies with the IEEE-802.3-2008 standard for Ethernet communication. The ESP32-Ethernet-Kit board only supports the Reduced Media-Independent Interface (RMII). The allocation of the ESP32 pins to the RMII interface is shown in the table below.

| Pin Name | Function 6       | RMII (int_osc) | RMII (ext_osc) |

|----------|------------------|----------------|----------------|

| GPIO0    | EMAC_TX_CLK      | CLK_OUT(O)     | EXT_OSC_CLK(I) |

| GPIO21   | EMAC_TX_EN       | TX_EN(O)       | TX_EN(O)       |

| GPIO19   | EMAC_TXD0        | TXD[0](O)      | TXD[0](O)      |

| GPIO22   | EMAC_TXD1        | TXD[1](O)      | TXD[1](O)      |

| GPIO27   | EMAC_RX_DV       | CRS_DV(I)      | CRS_DV(I)      |

| GPIO25   | EMAC_RXD0        | RXD[0](I)      | RXD[0](I)      |

| GPIO26   | EMAC_RXD1        | RXD[1](I)      | RXD[1](I)      |

| GPIO16   | EMAC_CLK_OUT     | CLK_OUT(O)     | _              |

| GPIO17   | EMAC_CLK_OUT_180 | CLK_OUT_180(O) | _              |

| Any GPIO | _                | MDC(O)         | MDC(O)         |

| Any GPIO | _                | MDIO(IO)       | MDIO(IO)       |

|          |                  |                |                |

Table 8: Ethernet MAC

DAMI C.

For an Ethernet solution, it is recommended to use GPIO0 as the clock input. Be aware that GPIO0 also acts as a strapping pin and it can be affected by the clock during chip power-up and may enter download mode as a result. Therefore, make sure you have turned off the clock output on the PHY side before powering up the chip. The ESP32-Ethernet-Kit board uses GPIO to control PHY's reset pin and turn off the clock output. However, not all PHYs support this design, so it is crucial to verify functionality during testing. If this design cannot be implemented, consider alternative methods to ensure that GPIO0 remains unaffected during power-up. For a reference design please see ESP32-Ethernet-Kit User Guide.

If you need to use Wi-Fi and Ethernet simultaneously, do not use the internal APLL clock to generate the RMII clock, as this can lead to clock instability. Instead, use the RMII clock from the PHY side or an external clock source. For further details, please refer to ESP32-Ethernet-Kit User Guide > RMII Clock Selection.

## 1.4 PCB Layout Design

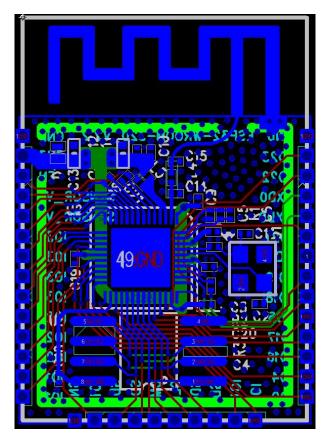

This chapter introduces the key points of how to design an ESP32 PCB layout using an ESP32 module (see Figure ESP32 Reference PCB Layout) as an example.

Fig. 14: ESP32 Reference PCB Layout

### 1.4.1 General Principles of PCB Layout for the Chip

It is recommended to use a four-layer PCB design:

- Layer 1 (TOP): Signal traces and components.

- Layer 2 (GND): No signal traces here to ensure a complete GND plane.

- Layer 3 (POWER): GND plane should be applied to better isolate the RF and crystal. Route power traces and a few signal traces on this layer, provided that there is a complete GND plane under the RF and crystal.

- Layer 4 (BOTTOM): Route a few signal traces here. It is not recommended to place any components on this layer.

A two-layer PCB design can also be used:

- Layer 1 (TOP): Signal traces and components.

- Layer 2 (BOTTOM): Do not place any components on this layer and keep traces to a minimum. Please make sure there is a complete GND plane for the chip, RF, and crystal.

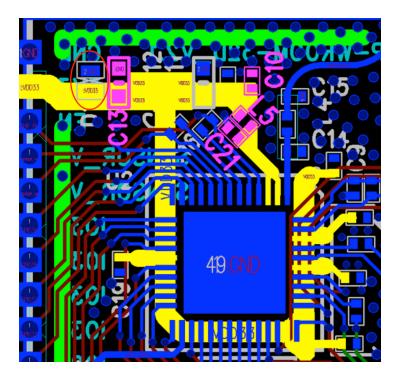

### 1.4.2 Power Supply

## Four-Layer PCB Design

Figure ESP32 Power Traces in a Four-Layer PCB Design shows the power traces in a four-layer PCB design.

Fig. 15: ESP32 Power Traces in a Four-Layer PCB Design

- A four-layer PCB design is recommended. Whenever possible, route the power traces on the inner layers (not the ground layer) and connect them to the chip pins through vias. There should be at least two vias if the main power traces need to cross layers. The drill diameter on other power traces should be no smaller than the width of the power traces.

- The 3.3 V power traces, highlighted in yellow, are routed as shown in Figure *ESP32 Power Traces in a Four-Layer PCB Design*. The width of the main power traces should be no less than 25 mil. The width of VDD3P3 power traces should be no less than 20 mil. The recommended width of other power traces is 10 mil. Ensure the power traces are surrounded by ground copper.

- The red circles in *ESP32 Power Traces in a Four-Layer PCB Design* show ESD protection diodes. Place them close to the power input. Add a 10 µF capacitor before the power trace enters the chip. You can also add a 0.1 µF or 1 µF capacitor in parallel. After that, the power trace can branch out in a star-shaped layout to reduce coupling between different power pins.

- The power supply for pin2 and pin3 is RF related, so please place a 10  $\mu$ F capacitor for each pin. You can also add a 0.1  $\mu$ F or 1  $\mu$ F capacitor in parallel.

- Add a CLC/LC filter circuit near pin2 and pin3 to suppress high-frequency harmonics. The power trace can be routed at a 45-degree angle to maintain distance from adjacent RF traces. Except for the 10 μF capacitor, it is recommended to use 0201 components. This allows the filter circuit for pin2 and pin3 to be placed closer to the pins, with a GND isolation layer separating them from surrounding RF and GPIO traces, while also maximizing the placement of ground vias. Using 0201 components enables placing a via to the bottom layer at the first capacitor near the chip, while maintaining a keep-out area on other layers, further reducing harmonic interference. See Figure ESP32 Power Traces in a Four-Layer PCB Design.

- In Figure *ESP32 Power Traces in a Four-Layer PCB Design*, the 10 µF capacitor is shared by the analog power supply VDD3P3, and the power entrance since the analog power is close to the chip power entrance. If the chip power entrance is not near VDD3P3, it is recommended to add a 10 µF capacitor to both the chip power entrance and VDD3P3.

- Place appropriate decoupling capacitors at the rest of the power pins. Ground vias should be added close to the capacitor's ground pad to ensure a short return path.

- The ground pad at the bottom of the chip should be connected to the ground plane through at least nine ground vias.

- The ground pads of the chip and surrounding circuit components should make full contact with the ground copper pour rather than being connected via traces.

- If you need to add a thermal pad EPAD under the chip on the bottom of the module, it is recommended to employ a square grid on the EPAD, cover the gaps with solder paste, and place ground vias in the gaps, as shown in Figure ESP32 Power Traces in a Four-Layer PCB Design. This helps effectively reduce solder leakage issues when soldering the module EPAD to the substrate.

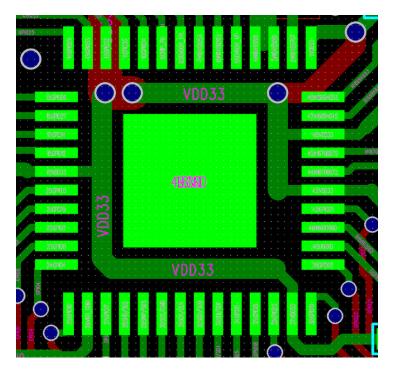

#### **Two-Layer PCB Design**

Figure ESP32 Power Traces in a Two-Layer PCB Design shows the power traces in a two-layer PCB design.

Fig. 16: ESP32 Power Traces in a Two-Layer PCB Design

- For a two-layer design, ensure to provide a continuous reference ground for the chip, RF, and crystal oscillator, as shown in the figure above.

- In the figure above, the trace VDD33 represents the 3.3 V power trace. Unlike a four-layer design, the power trace should be routed on the top layer as much as possible. Therefore, the thermal pad in the center of the chip should be reduced in size, allowing the power trace to pass between the signal pads and the thermal pad. Vias to the bottom layer should only be used when absolutely necessary.

- Other layout considerations are the same as for a four-layer design.

#### 1.4.3 Crystal

Figure ESP32 Crystal Layout (with Keep-out Area on Top Layer) shows a reference PCB layout where the crystal is connected to the ground through vias and a keep-out area is maintained around the crystal on the top layer for ground isolation.

The layout of the crystal should follow the guidelines below:

- Ensure a complete GND plane for the RF, crystal, and chip.

- The crystal should be placed far from the clock pin to avoid interference on the chip. The gap should be at least 2.7 mm. It is good practice to add high-density ground vias stitching around the clock trace for better isolation.

Fig. 17: ESP32 Crystal Layout (with Keep-out Area on Top Layer)

- There should be no vias for the clock input and output traces.

- Components in series to the crystal trace should be placed close to the chip side.

- The external matching capacitors should be placed on the two sides of the crystal, preferably at the end of the clock trace, but not connected directly to the series components. This is to make sure the ground pad of the capacitor is close to that of the crystal.

- Do not route high-frequency digital signal traces under the crystal. It is best not to route any signal trace under the crystal. The vias on the power traces on both sides of the crystal clock trace should be placed as far away from the clock trace as possible, and the two sides of the clock trace should be surrounded by ground copper.

- As the crystal is a sensitive component, do not place any magnetic components nearby that may cause interference, for example large inductance component, and ensure that there is a clean large-area ground plane around the crystal.

#### 1.4.4 RF

#### **RF** Layout on Four-layer PCB

The RF trace is routed as shown highlighted in pink in Figure ESP32 RF Layout in a Four-layer PCB Design.

The RF layout should meet the following guidelines:

- The RF trace should have a 50  $\Omega$  characteristic impedance. The reference plane is the layer next to the chip. For designing the RF trace at 50  $\Omega$  impedance, you could refer to the PCB stack-up design shown below.

- A CLC matching circuit is required for chip tuning. Please use 0201 components and place them close to the pin in a zigzag. In other words, the two capacitors should not be oriented in the same direction to minimize interference.

- Add a stub on the grounding capacitor near the chip side in the CLC matching circuit to suppress the second harmonics. It is preferable to keep the stub length 15 mil, and determine the stub width according to the PCB stack-up so that the characteristic impedance of the stub is  $100 \Omega \pm 10\%$ . In addition, please connect the stub

Fig. 18: ESP32 RF Layout in a Four-layer PCB Design

| Thickness (mm) | Impedance (Ohm) | Gap (mil) | Width (mil) | Gap (mil) |

|----------------|-----------------|-----------|-------------|-----------|

| -              | 50              | 12.2      | 12.6        | 12.2      |

| Stack up  | Material             | Base copper (oz) | Finished<br>Layer<br>Thickness<br>(mil) | DK  |

|-----------|----------------------|------------------|-----------------------------------------|-----|

| СМ        |                      |                  | 0.4                                     | 4   |

| L1_Top    | Finished Copper 1 oz | 0.33             | 0.8 ( Min )                             |     |

| PP        | 7628 TG150 RC50%     |                  | 8.22                                    | 4.6 |

| L2_Gnd    |                      | 1                | 1.2                                     |     |

| Core      | Core                 |                  | Adjustable                              | 4.6 |

| L3_Power  |                      | 1                | 1.2                                     |     |

| PP        | 7628 TG150 RC50%     |                  | 8.22                                    | 4.6 |

| L4_Bottom | Finished Copper 1 oz | 0.33             | 0.8 ( Min )                             |     |

| SM        |                      |                  | 0.4                                     | 4   |

Fig. 19: ESP32 PCB Stack-up Design

- via to the third layer, and maintain a keep-out area on the first and second layers. The trace highlighted in figure below is the stub. Note that a stub is not required for package types of 0402 and above.

- For PCB antennas, make sure to validate them through both simulation and real-world testing on a development board. It is recommended to include an additional CLC matching circuit for antenna tuning. Place this circuit as close to the antenna as possible.

Fig. 20: ESP32 Stub in a Four-layer PCB Design

- The RF trace should have a consistent width and not branch out. It should be as short as possible with dense ground vias around for interference shielding.

- The RF trace should be routed on the outer layer without vias, i.e., should not cross layers. The RF trace should be routed at a 135° angle, or with circular arcs if trace bends are required.

- The ground plane on the adjacent layer needs to be complete. Do not route any traces under the RF trace whenever possible.

- There should be no high-frequency signal traces routed close to the RF trace. The RF antenna should be placed away from high-frequency components, such as crystals, DDR SDRAM, high-frequency clocks, etc. In addition, the USB port, USB-to-serial chip, UART signal lines (including traces, vias, test points, header pins, etc.) must be as far away from the antenna as possible. The UART signal line should be surrounded by ground copper and ground vias.

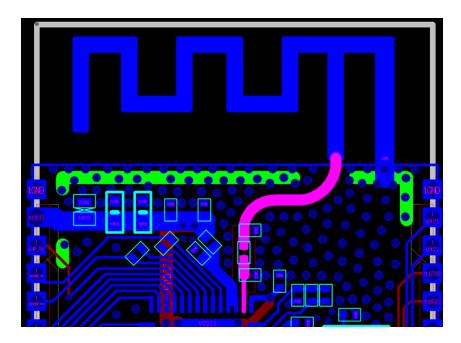

#### RF Layout on Two-layer PCB

In a two-layer PCB design, the RF trace is routed as shown highlighted in pink in Figure ESP32 RF Layout in a Two-layer PCB Design. The width of the RF trace should be greater than that of the RF trace in a four-layer board and is normally over 20 mil. The actual width depends on the impedance formula where impedance-relevant parameters may vary depending on the number of PCB layers.

Other good practices for routing RF traces in four-layer PCB designs still apply to two-layer board designs.

#### 1.4.5 Flash and PSRAM

The layout for flash and PSRAM should follow the guidelines below:

- Place the zero-ohm resistors in series on the SPI lines close to ESP32.

- Route the SPI traces on the inner layer (e.g., the third layer) whenever possible, and add ground copper and ground vias around the clock and data traces of SPI separately.

- If the flash and PSRAM are located far from ESP32, it is recommended to place appropriate decoupling capacitors both at VDD SPI and near the flash and PSRAM.

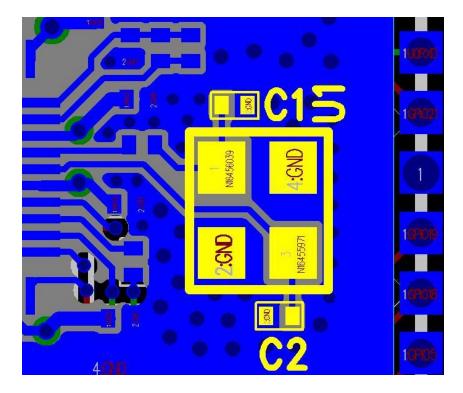

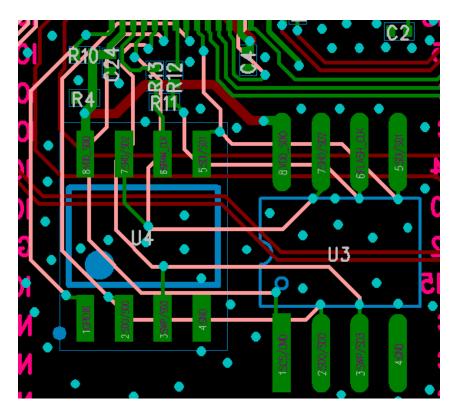

Figure ESP32 Flash and PSRAM Layout shows an example of flash (U3) and PSRAM (U4) layout.

Fig. 21: ESP32 RF Layout in a Two-layer PCB Design

Fig. 22: ESP32 Flash and PSRAM Layout

#### 1.4.6 External RC

External resistors and capacitors should be placed close to the chip pins, and there should be no vias around the traces. Please ensure that 10 nF capacitors are placed close to the pins.

#### 1.4.7 **UART**

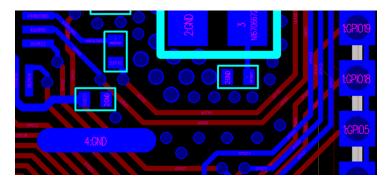

Figure ESP32 UART Layout shows the UART layout.

Fig. 23: ESP32 UART Layout

The UART layout should meet the following guidelines:

- The series resistor on the U0TXD trace needs to be placed close to the chip side and away from the crystal.

- The U0TXD and U0RXD traces on the top layer should be as short as possible.

- The UART trace should be surrounded by ground copper and ground vias stitching.

## 1.4.8 General Principles of PCB Layout for Modules (Positioning a Module on a Base Board)

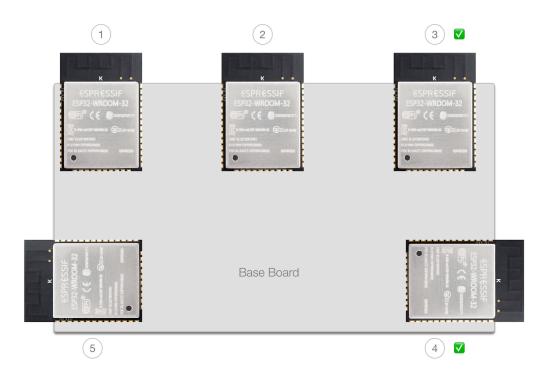

If module-on-board design is adopted, attention should be paid while positioning the module on the base board. The interference of the baseboard on the module's antenna performance should be minimized.

It is suggested to place the module's on-board PCB antenna outside the base board, and the feed point of the antenna closest to the board. In the following example figures, positions with mark  $\checkmark$  are strongly recommended, while positions without a mark are not recommended.

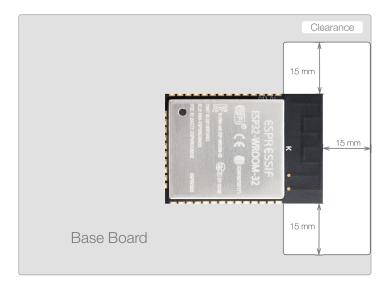

If the PCB antenna cannot be placed outside the board, please ensure a clearance of at least 15 mm (in all directions) around the antenna area (no copper, routing, or components on it), and place the feed point of the antenna closest to the board. If there is a base board under the antenna area, it is recommended to cut it off to minimize its impact on the antenna. Figure *Keepout Zone for ESP32 Module's Antenna on the Base Board* shows the suggested clearance for modules whose antenna feed point is on the right.

When designing an end product, attention should be paid to the interference caused by the housing of the antenna and it is recommended to carry out RF verification. It is necessary to test the throughput and communication signal range of the whole product to ensure the product's actual RF performance.

#### 1.4.9 **SDIO**

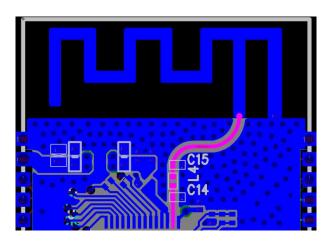

The SDIO layout should follow the guidelines below:

- Minimize parasitic capacitance of SDIO traces as they involve high-speed signals.

- The trace lengths for SDIO\_CMD and SDIO\_DATA0  $\sim$  SDIO\_DATA3 should be within  $\pm$  50 mil of the SDIO\_CLK trace length. Use serpentine routing if necessary.

- For SDIO routing, maintain a 50  $\Omega$  single-ended impedance with a tolerance of  $\pm 10\%$ .

Fig. 24: Placement of ESP32 Modules on Base Board (antenna feed point on the right)

Fig. 25: Keepout Zone for ESP32 Module's Antenna on the Base Board

- Keep the total trace length from SDIO GPIOs to the master SDIO interface as short as possible, ideally within 2000 mil.

- Ensure that SDIO traces do not cross layers. Besides, a reference plane (preferably a ground plane) must be placed beneath the traces, and continuity of the reference plane must be ensured.

- It is recommended to surround the SDIO\_CLK trace with ground copper.

#### 1.4.10 Touch Sensor

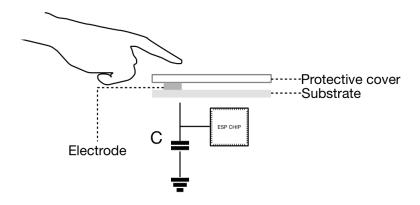

ESP32 offers up to 10 capacitive IOs that detect changes in capacitance on touch sensors due to finger contact or proximity. The chip's internal capacitance detection circuit features low noise and high sensitivity. It allows to use touch pads with smaller area to implement the touch detection function. You can also use the touch panel array to detect a larger area or more test points.

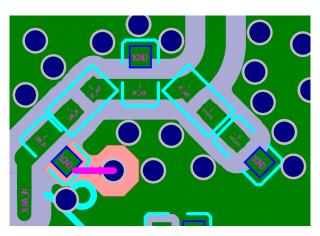

Figure ESP32 Typical Touch Sensor Application depicts a typical touch sensor application.

Fig. 26: ESP32 Typical Touch Sensor Application

To prevent capacitive coupling and other electrical interference to the sensitivity of the touch sensor system, the following factors should be taken into account.

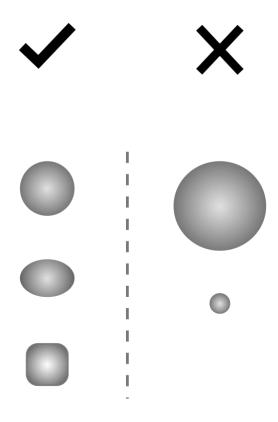

#### **Electrode Pattern**

The proper size and shape of an electrode improves system sensitivity. Round, oval, or shapes similar to a human fingertip are commonly applied. Large size or irregular shape might lead to incorrect responses from nearby electrodes.

Figure *ESP32 Electrode Pattern Requirements* shows the proper and improper size or shape of electrode. Please note that the examples illustrated in the figure are not of actual scale. It is suggested to use a human fingertip as reference.

#### **PCB** Layout

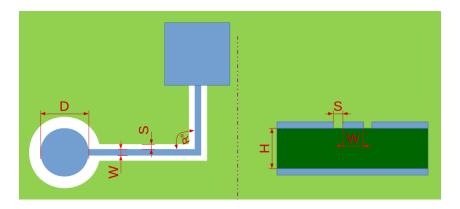

Figure ESP32 Sensor Track Routing Requirements illustrates the general guidelines to routing traces. Specifically,

- The trace should be as short as possible and no longer than 300 mm.

- The trace width (W) can not be larger than 0.18 mm (7 mil).

- The alignment angle (R) should not be less than 90°.

- The trace-to-ground gap (S) should be in the range of 0.5 mm to 1 mm.

- The electrode diameter (D) should be in the range of 8 mm to 15 mm.

- Hatched ground should be added around the electrodes and traces.

- The traces should be isolated well and routed away from that of the antenna.

Note: For more details on the hardware design of the touch sensor, please refer to Touch Sensor Application Note.

Fig. 27: ESP32 Electrode Pattern Requirements

Fig. 28: ESP32 Sensor Track Routing Requirements

#### 1.4.11 Typical Layout Problems and Solutions

#### The voltage ripple is not large, but the TX performance of RF is rather poor.

**Analysis:** The voltage ripple has a strong impact on the RF TX performance. It should be noted that the ripple must be tested when ESP32 is in the normal working mode. The ripple increases when the power gets high in a different mode.

Generally, the peak-to-peak value of the ripple should be <80 mV when ESP32 sends MCS7@11n packets, and <120 mV when ESP32 sends 11 MHz@11b packets.

**Solution:** Add a 10  $\mu$ F filter capacitor to the branch of the power trace (the branch powering the chip's analog power pin). The 10  $\mu$ F capacitor should be as close to the analog power pin as possible for small and stable voltage ripples.

#### When ESP32 sends data packages, the voltage ripple is small, but RF TX performance is poor.

**Analysis:** The RF TX performance can be affected not only by voltage ripples, but also by the crystal itself. Poor quality and big frequency offsets of the crystal decrease the RF TX performance. The crystal clock may be corrupted by other interfering signals, such as high-speed output or input signals. In addition, high-frequency signal traces, such as the SDIO traces and UART traces under the crystal, could also result in the malfunction of the crystal. Besides, sensitive components or radiating components, such as inductors and antennas, may also decrease the RF performance.

**Solution:** This problem is caused by improper layout for the crystal and can be solved by re-layout. Please refer to Section *Crystal* for details.

## When ESP32 sends data packages, the power value is much higher or lower than the target power value, and the EVM is relatively poor.

**Analysis:** The disparity between the tested value and the target value may be due to signal reflection caused by the impedance mismatch on the transmission line connecting the RF pin and the antenna. Besides, the impedance mismatch will affect the working state of the internal PA, making the PA prematurely access the saturated region in an abnormal way. The EVM becomes poor as the signal distortion happens.

**Solution:** Match the antenna's impedance with the  $\pi$ -type circuit on the RF trace, so that the impedance of the antenna as seen from the RF pin matches closely with that of the chip. This reduces reflections to the minimum.

#### TX performance is not bad, but the RX sensitivity is low.

**Analysis:** Good TX performance indicates proper RF impedance matching. Poor RX sensitivity may result from external coupling to the antenna. For instance, the crystal signal harmonics could couple to the antenna. If the TX and RX traces of UART cross over with RF trace, they will affect the RX performance, as well. If there are many high-frequency interference sources on the board, signal integrity should be considered.

**Solution:** Keep the antenna away from crystals. Do not route high-frequency signal traces close to the RF trace. Please refer to Section *RF* for details.

## 1.5 Hardware Development

#### **1.5.1** ESP32 Modules

For a list of ESP32 modules please check the Modules section on Espressif's official website.

For module reference designs please refer to:

· Download links

**Note:** Use the following tools to open the files in module reference designs:

- .DSN files: OrCAD Capture V16.6

- .pcb files: Pads Layout VX.2. If you cannot open the .pcb files, please try importing the .asc files into your software to view the PCB layout.

## 1.5.2 ESP32 Development Boards

For a list of the latest designs of ESP32 boards please check the Development Boards section on Espressif's official website.

#### 1.5.3 Download Guidelines

You can download firmware to ESP32 via UART.

To download via UART:

- 1. Before the download, make sure to set the chip or module to Joint Download Boot mode, according to Table *Boot Mode Control*.

- 2. Power up the chip or module and check the log via the UART0 serial port. If the log shows "waiting for download", the chip or module has entered Joint Download Boot mode.

- 3. Download your firmware into flash via UART using the Flash Download Tool.

- 4. After the firmware has been downloaded, pull GPIO0 high or leave it floating to make sure that the chip or module enters SPI Boot mode.

- 5. Power up the chip or module again. The chip will read and execute the new firmware during initialization.

#### Note:

- It is advised to download the firmware only after the "waiting for download" log shows via the serial port.

- Serial tools cannot be used simultaneously with the Flash Download Tool on one COM port.

### 1.6 Related Documentation and Resources

- Chip Datasheet (PDF)

- Technical Reference Manual (PDF)

- Chip Errata (PDF)

- ESP32 Chip Variants

- Modules

- ESP32 Development Boards

- Espressif KiCad Library

- ESP Product Selector

- Regulatory Certificates

- User Forum (Hardware)

• Technical Support

## 1.7 Glossary

The glossary contains terms and acronyms that are used in this document.

| Term              | Description                                                                                 |

|-------------------|---------------------------------------------------------------------------------------------|

| CLC               | Capacitor-Inductor-Capacitor                                                                |

| DDR SDRAM         | Double Data Rate Synchronous Dynamic Random-Access Memory                                   |

| ESD               | Electrostatic Discharge                                                                     |

| LC                | Inductor-Capacitor                                                                          |

| PA                | Power Amplifier                                                                             |

| RC                | Resistor-Capacitor                                                                          |

| RTC               | Real-Time Clock                                                                             |

| Zero-ohm resistor | A zero-ohm resistor acts as a placeholder in the circuit, allowing for the replacement with |

|                   | a higher-ohm resistor based on specific design requirements.                                |

## 1.8 Revision History

Table 9: Revision History

| Date       | Ver-<br>sion | Release Notes                                                                                                                                                                                                                                                                                                |

|------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2025-05-23 | v1.7         | PCB Layout Design     Section SDIO: Updated descriptions about the SDIO layout guidelines     Section Crystal: Updated descriptions about the crystal layout guidelines                                                                                                                                      |

| 2024-12-27 | v1.6         | Schematic Checklist     Section RTC Clock Source (Optional): Updated descriptions about the 32.768 crystal and chip revisions                                                                                                                                                                                |

| 2024-12-09 | v1.5         | Hardware Development     Section ESP32 Modules: Added download links to module reference designs                                                                                                                                                                                                             |

| 2024-11-15 | v1.4         | Schematic Checklist     Section SPI: Newly added section                                                                                                                                                                                                                                                     |

| 2024-10-15 | v1.3         | Schematic Checklist     Section Ethernet MAC: Newly added section     Section UART: Updated the AT related description                                                                                                                                                                                       |

| 2024-01-09 | v1.2         | • Schematic Checklist  - Section RF Tuning: Updated RF matching description                                                                                                                                                                                                                                  |

| 2023-12-25 | v1.1         | <ul> <li>PCB Layout Design         <ul> <li>Section Crystal: Updated crystal PCB layout</li> </ul> </li> </ul>                                                                                                                                                                                               |

| 2023-12-22 | v1.0         | Migrated ESP32 Hardware Design Guidelines from PDF to HTML format. During the migration from PDF to HTML format, minor updates, improvements, and clarifications were made throughout the documentation. If you would like to check previous versions of the document, please submit documentation feedback. |

## 1.9 Disclaimer and Copyright Notice

Information in this document, including URL references, is subject to change without notice.

All third party's information in this document is provided as is with no warranties to its authenticity and accuracy.

No warranty is provided to this document for its merchantability, non-infringement, fitness for any particular purpose, nor does any warranty otherwise arising out of any proposal, specification or sample.

All liability, including liability for infringement of any proprietary rights, relating to use of information in this document is disclaimed. No licenses express or implied, by estoppel or otherwise, to any intellectual property rights are granted herein.

The Wi-Fi Alliance Member logo is a trademark of the Wi-Fi Alliance. The Bluetooth logo is a registered trademark of Bluetooth SIG.

All trade names, trademarks and registered trademarks mentioned in this document are property of their respective owners, and are hereby acknowledged.