Interrupts play a crucial role in computer devices by allowing the processor to react quickly to events or requests from external devices or software. In this article, we are going to discuss every point about interruption and its various types in detail.

What is an Interrupt?

The interrupt is a signal emitted by hardware or software when a process or an event needs immediate attention. It alerts the processor to a high-priority process requiring interruption of the current working process. In I/O devices one of the bus control lines is dedicated for this purpose and is called the Interrupt Service Routine (ISR).

When a device raises an interrupt at let's say process i,e., the processor first completes the execution of instruction i. Then it loads the Program Counter (PC) with the address of the first instruction of the ISR. Before loading the Program Counter with the address, the address of the interrupted instruction is moved to a temporary location. Therefore, after handling the interrupt the processor can continue with process i+1.

While the processor is handling the interrupts, it must inform the device that its request has been recognized so that it stops sending the interrupt request signal. Also, saving the registers so that the interrupted process can be restored in the future, increases the delay between the time an interrupt is received and the start of the execution of the ISR. This is called Interrupt Latency.

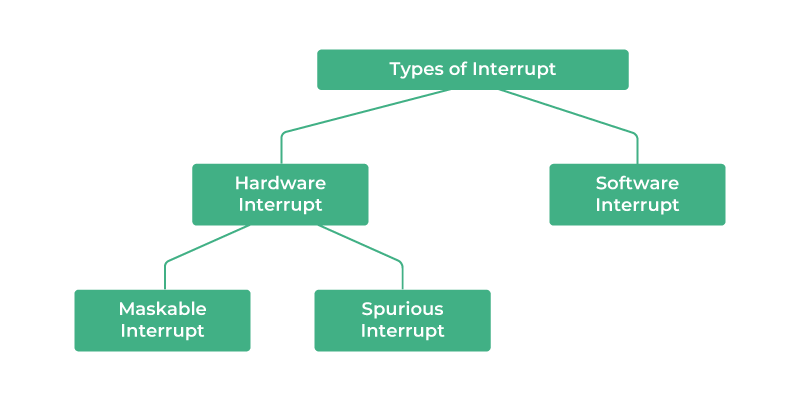

Types of Interrupt

Event-related software or hardware can trigger the issuance of interrupt signals. These fall into one of two categories: software interrupts or hardware interrupts.

1. Software Interrupts

A sort of interrupt called a software interrupt is one that is produced by software or a system as opposed to hardware. Traps and exceptions are other names for software interruptions. They serve as a signal for the operating system or a system service to carry out a certain function or respond to an error condition. Generally, software interrupts occur as a result of specific instructions being used or exceptions in the operation. In our system, software interrupts often occur when system calls are made. In contrast to the fork() system call, which also generates a software interrupt, division by zero throws an exception that results in the software interrupt.

A particular instruction known as an "interrupt instruction" is used to create software interrupts. When the interrupt instruction is used, the processor stops what it is doing and switches over to a particular interrupt handler code. The interrupt handler routine completes the required work or handles any errors before handing back control to the interrupted application.

Types of Interrupt

Types of Interrupt2. Hardware Interrupts

In a hardware interrupt, all the devices are connected to the Interrupt Request Line. A single request line is used for all the n devices. To request an interrupt, a device closes its associated switch. When a device requests an interrupt, the value of INTR is the logical OR of the requests from individual devices.

Hardware interrupts are further divided into two types of interrupt

- Maskable Interrupt: Hardware interrupts can be selectively enabled and disabled thanks to an inbuilt interrupt mask register that is commonly found in processors. A bit in the mask register corresponds to each interrupt signal; on some systems, the interrupt is enabled when the bit is set and disabled when the bit is clear, but on other systems, the interrupt is deactivated when the bit is set.

- Spurious Interrupt: A hardware interrupt for which there is no source is known as a spurious interrupt. This phenomenon might also be referred to as phantom or ghost interrupts. When a wired-OR interrupt circuit is connected to a level-sensitive processor input, spurious interruptions are typically an issue. When a system performs badly, it could be challenging to locate these interruptions.

Sequences of Events Involved in Handling an IRQ(Interrupt Request)

- Devices raise an IRQ.

- The processor interrupts the program currently being executed.

- The device is informed that its request has been recognized and the device deactivates the request signal.

- The requested action is performed.

- An interrupt is enabled and the interrupted program is resumed.

Flowchart of Interrupt Handling Mechanism

The Image below depicts the flowchart of interrupt handling mechanism

Interrupt Handling Mechanism

Interrupt Handling Mechanism- Step 1:- Any time that an interrupt is raised, it may either be an I/O interrupt or a system interrupt.

- Step 2:- The current state comprising registers and the program counter is then stored in order to conserve the state of the process.

- Step 3:- The current interrupt and its handler is identified through the interrupt vector table in the processor.

- Step 4:- This control now shifts to the interrupt handler, which is a function located in the kernel space.

- Step 5:- Specific tasks are performed by Interrupt Service Routine (ISR) which are essential to manage interrupt.

- Step 6:- The status from the previous session is retrieved so as to build on the process from that point.

- Step 7:- The control is then shifted back to the other process that was pending and the normal process continues.

Managing Multiple Devices

When more than one device raises an interrupt request signal, then additional information is needed to decide which device to be considered first. The following methods are used to decide which device to select: Polling, Vectored Interrupts, and Interrupt Nesting. These are explained below.

- Polling: In polling, the first device encountered with the IRQ bit set is the device that is to be serviced first. Appropriate ISR is called to service the same. It is easy to implement but a lot of time is wasted by interrogating the IRQ bit of all devices.

- Vectored Interrupts: In vectored interrupts, a device requesting an interrupt identifies itself directly by sending a special code to the processor over the bus. This enables the processor to identify the device that generated the interrupt. The special code can be the starting address of the ISR or where the ISR is located in memory and is called the interrupt vector.

- Interrupt Nesting: In this method, the I/O device is organized in a priority structure. Therefore, an interrupt request from a higher-priority device is recognized whereas a request from a lower-priority device is not. The processor accepts interrupts only from devices/processes having priority.

Processors' priority is encoded in a few bits of PS (Process Status register). It can be changed by program instructions that are written into the PS. The processor is in supervised mode only while executing OS routines. It switches to user mode before executing application programs.

Interrupt Priority Schemes

Interrupt priority schemes are used in microprocessors and microcontrollers to manage multiple interrupt requests (IRQs). These schemes ensure that more urgent tasks are processed before less important ones, making them essential for real-time systems and efficient interrupt handling.

Types of Interrupt Priority Schemes

- Fixed Priority Scheme: In this scheme, each interrupt has a predetermined priority level. The interrupt with the highest priority is handled first. If two interrupts occur simultaneously, the one with the higher priority is serviced. Example: Interrupt A (priority 1) is serviced before Interrupt B (priority 2).

- Dynamic Priority Scheme: In a dynamic priority scheme, the priority of an interrupt can change based on system conditions. This helps prioritize real-time or critical tasks over others. Example: A system may increase the priority of a sensor interrupt based on its importance at a particular moment.

- Vectored Interrupt Scheme: Here, each interrupt has a specific memory address (vector). The processor jumps to this address to handle the interrupt, and the interrupt with the highest priority is processed first. Example: The system uses memory addresses to quickly handle the most urgent interrupts.

- Priority Masking: This scheme allows lower-priority interrupts to be temporarily disabled, ensuring that high-priority interrupts are handled immediately without delay. Example: If Interrupt A is more critical than Interrupt B, Interrupt B may be masked until Interrupt A is processed.

- Round-Robin Priority Scheme: In this scheme, interrupts are processed in a cyclic order, ensuring each interrupt gets handled fairly, especially when all interrupts have the same priority. Example:Interrupts A, B, and C are handled in a round-robin manner.

What is Interrupt Latency?

The amount of time between the generation of an interrupt and its handling is known as interrupt latency. The number of created interrupts, the number of enabled interruptions, the number of interrupts that may be handled, and the time required to handle each interrupt all affect interrupt latency. When the device generating the interrupt needs a specific length of time to generate the interrupt, interrupt latency is required. For instance, if a printer is printing paper, the computer needs to stop the printing program and wait for the document to finish printing. The interrupt latency is the amount of time the computer has to stop the program from operating.

Interrupt Latency

Interrupt LatencyHow CPU React when Interrupt Occurs?

- Interrupt Detection: The CPU continuously video displays unit interrupt lines or alerts from diverse resources, consisting of hardware gadgets or software program commands, to hit upon interrupt requests.

- Interrupt Acknowledgment: Upon detecting an interrupt request, the CPU acknowledges the interrupt using sending an acknowledgment sign to the interrupting device or software program.

- Interrupt Handling: The CPU identifies the form of interrupt primarily based on its supply, together with a hardware interrupt from a device or a software interrupt from a training. It then seems the cope with the corresponding interrupt handler habitual within the interrupt vector desk.

- Context Saving: Before moving manipulate to the interrupt handler ordinary, the CPU saves the present-day execution context, inclusive of the program counter (PC), processor state, and any applicable sign-in contents, onto the stack or in the devoted garage.

- Transfer Control: The CPU transfers manipulation to the interrupt handler ordinary with the aid of placing this system counter (PC) to the address of the handler habitual retrieved from the interrupt vector desk.

- Interrupt Servicing: The interrupt handler habitual executes to carrier the interrupt. It plays responsibilities to interrupt, such as reading facts from a device, processing enter/output operations, or coping with a software program request.

Triggering Methods

Every interrupt signal input is intended to be activated by a certain signal edge (level change) or a logic signal level. Level-sensitive inputs make constant requests for processor attention as long as they are treated with a specific logic level (high or low). Edge-sensitive inputs are responsive to signal edges; a service request will latch on to a specific (rising or falling) edge. When the interrupt handler runs, the CPU resets the latch.

- Level-Trigger: The interrupt signal must be held at its specific active logic level (high or low) to request a level-triggered interrupt. A level-triggered interrupt is triggered when a device drives the signal to the active level and maintains it there. When the CPU instructs it to do so, usually after the device has been serviced, it denies the signal.

- Edge-Trigger: An interrupt that is caused by a level change on the interrupt line—either a rising or lowering edge—is known as an edge-triggered interrupt (low to high). A pulse is driven onto the line and released to its inactive state by a device that wishes to indicate an interrupt. It can be necessary to use specialized hardware to detect the pulse if polled I/O is unable to pick it up due to its short duration.

Benefits of Interrupt

- Real-time Responsiveness: Interrupts permit a system to reply promptly to outside events or signals, permitting real-time processing.

- Efficient Resource usage: Interrupt-driven structures are more efficient than system that depend on busy-waiting or polling strategies. Instead of continuously checking for the incidence of event, interrupts permit the processor to remain idle until an event occurs, conserving processing energy and lowering energy intake.

- Multitasking and Concurrency: Interrupts allow multitasking with the aid of allowing a processor to address multiple tasks concurrently.

- Improved system Throughput: By coping with occasions asynchronously, interrupts allow a device to overlap computation with I/O operations or other responsibilities, maximizing system throughput and universal overall performance.

Conclusion

- The events known as interrupts alert the CPU to handle the request.

- Both software and hardware can create interruptions.

- Maskable and non-maskable interrupts are the two categories of hardware interrupts.

- Generally speaking, exceptions and special instructions like fork() are what trigger software interrupts.

- After completing the service request and handling the interruption, the CPU continues the process where it left off.