04 sequentialbasics 1

- 1. Digital Design: An Embedded Systems Approach Using Verilog Chapter 4 Sequential Basics Portions of this work are from the book, Digital Design: An Embedded Systems Approach Using Verilog, by Peter J. Ashenden, published by Morgan Kaufmann Publishers, Copyright 2007 Elsevier Inc. All rights reserved.

- 2. Verilog Digital Design — Chapter 4 — Sequential Basics 2 Sequential Basics Sequential circuits Outputs depend on current inputs and previous inputs Store state: an abstraction of the history of inputs Usually governed by a periodic clock signal

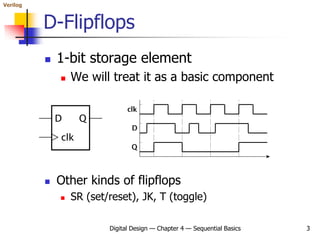

- 3. Verilog Digital Design — Chapter 4 — Sequential Basics 3 D-Flipflops 1-bit storage element We will treat it as a basic component Other kinds of flipflops SR (set/reset), JK, T (toggle)

- 4. Verilog Digital Design — Chapter 4 — Sequential Basics 4 Registers Store a multi-bit encoded value One D-flipflop per bit Stores a new value on each clock cycle wire [n:0] d; reg [n:0] q; ... always @(posedge clk) q <= d; event list nonblocking asignment n n n n

- 5. Verilog Digital Design — Chapter 4 — Sequential Basics 5 Pipelines Using Registers Total delay = Delay1 + Delay2 + Delay3 Clock period = Delay1 + Delay2 + Delay3 Interval between outputs > Total delay Clock period = max(Delay1, Delay2, Delay3) Total delay = 3 × clock period Interval between outputs = 1 clock period combin- ational circuit 1 combin- ational circuit 2 combin- ational circuit 3 combin- ational circuit 1 combin- ational circuit 2 combin- ational circuit 3

- 6. Verilog 6 Pipeline Example Compute the average of corresponding numbers in three input streams New values arrive on each clock edge module average_pipeline ( output reg signed [0:13] avg, input signed [0:13] a, b, c, wire signed [0:14] a_plus_b; Wire signed [0:15] sum; wire signed [0:22] sum_div_3; reg signed [0:14] saved_a_plus_b Reg signed [0:13] saved_c Reg [0:15] saved_sum; ... input clk );

- 7. Verilog Digital Design — Chapter 4 — Sequential Basics 7 Pipeline Example ... assign a_plus_b = a + b; always @(posedge clk) begin // Pipeline register 1 saved_a_plus_b <= a_plus_b; saved_c <= c; end assign sum = saved_a_plus_b + saved_c; always @(posedge clk) // Pipeline register 2 saved_sum <= sum; assign sum_div_3 = saved_sum * 7'b0101010; always @(posedge clk) // Pipeline register 3 avg <= sum_div_3; endmodule

- 8. Verilog Blockdiagram Digital Design — Chapter 4 — Sequential Basics 8 a+b Divide by 3 Saved a+b a+b+c Saved c

![Verilog

Digital Design — Chapter 4 — Sequential Basics 4

Registers

Store a multi-bit encoded value

One D-flipflop per bit

Stores a new value on

each clock cycle

wire [n:0] d;

reg [n:0] q;

...

always @(posedge clk)

q <= d;

event list

nonblocking

asignment

n

n n

n](https://image.slidesharecdn.com/04sequentialbasics-1-150716063739-lva1-app6892/85/04-sequentialbasics-1-4-320.jpg)

![Verilog

6

Pipeline Example

Compute the average of corresponding

numbers in three input streams

New values arrive on each clock edge

module average_pipeline ( output reg signed [0:13] avg,

input signed [0:13] a, b, c,

wire signed [0:14] a_plus_b;

Wire signed [0:15] sum;

wire signed [0:22] sum_div_3;

reg signed [0:14] saved_a_plus_b

Reg signed [0:13] saved_c

Reg [0:15] saved_sum;

...

input clk );](https://image.slidesharecdn.com/04sequentialbasics-1-150716063739-lva1-app6892/85/04-sequentialbasics-1-6-320.jpg)