2.3 sequantial logic circuit

- 1. 2.3 Build sequential logic circuit Combinational logic circuit Sequential logic circuit Flip-flop Build flip-flop using logic gates 1

- 2. Objectives: • 1 Define sequential logic circuit. • 2 Differentiate between combinational logic circuit and sequential logic circuit. • 3 Describe flip - flop. • 4 Identify various types of flip-flops. • 5 Build SR, JK, T and D flip – flop using logic gates. • 6 Draw the symbol and truth table of SR, JK, T and D flip – flop. 2

- 3. Sequential & Combinational logic circuit 1 Define sequential logic circuit. 2 Differentiate between combinational logic circuit and sequential logic circuit. 3

- 4. Difference between Combinational & Sequential logic circuit Combinational Logic Circuits Basic building blocks include: Sequential Logic Circuits Basic building blocks include FLIP-FLOPS: 4

- 5. Sequential S C Q logic circuit R Q' • Sequential logic is the type of digital system that does not only depend on current input, but also the previous history of the system. • For that reason sequential logic requires memory elements to function. • The building blocks used to construct devices that store data are called flip-flops. 5

- 6. Sequential logic circuit Sequential circuit have loops – these enable curcuits to receive feedback 6

- 7. Combinational logic circuit • Combinational logic is an interconnection of logic gates to generate a specificities logic function where the inputs result in an immediate output, having no memory or storage capabilities. • There are function only based on their inputs, and NOT based on clocks. 7

- 8. Combinational logic circuit Combinational circuit is combination of various logic gates 8

- 9. Flip-Flop 3 Describe flip - flop. 9

- 10. Flip-Flop • "Flip-flop" is the common name given to two-state devices which offer basic memory for sequential logic operations. • Flip-flops are heavily used for digital data storage and transfer and are commonly used in banks called "registers" for the storage of binary numerical data. 10

- 11. Flip-Flop • Flip-flop are basic storage/memory elements. • Flip-flop are essentially 1-bit storage devices. • Types of flip-flops are: • 1. SR Flip-flop • 2. JK Flip-flop • 3. D Flip-flop • 4. T Flip-flop • Application of flip-flop: • 1. Counter 4. Logic controller • 2. Register 5. Frequency Divider • 3. Memory 11

- 12. SR Flip-Flop 4 Identify various types of flip-flops. 5 Build SR, JK, T and D flip – flop using logic gates. 6 Draw the symbol and truth table of SR, JK, T and D flip – flop. 12

- 13. SR Flip-Flop S Q R Q' • The simplest binary storage device. • SR Flip-flop have 2 inputs (SET & RESET) and 2 outputs (Q & Q’). NOTE: Q & Q’ are compliments of each other • The SR flip flop is sometimes referred to as an SR latch. The Term latch refers to its use as a temporary memory storage device. 13

- 14. SR Flip-Flop Symbol: SR Flip-flop (Active HIGH) SR Flip-flop (Active HIGH) NOR gate Symbol 14

- 15. SR Flip-Flop Symbol: SR Flip-flop (Active LOW) SR Flip-flop (Active LOW) NAND gate Symbol 15

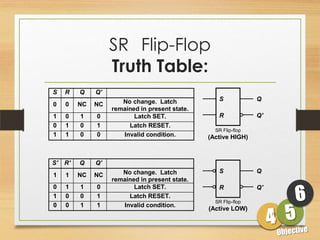

- 16. SR Flip-Flop Truth Table: S R Q Q' No change. Latch S Q 0 0 NC NC remained in present state. 1 0 1 0 Latch SET. R Q' 0 1 0 1 Latch RESET. SR Flip-flop 1 1 0 0 Invalid condition. (Active HIGH) S' R' Q Q' No change. Latch S Q 1 1 NC NC remained in present state. 0 1 1 0 Latch SET. R Q' 1 0 0 1 Latch RESET. SR Flip-flop 0 0 1 1 Invalid condition. (Active LOW) 16

- 17. SR Flip-Flop Timing Diagram: 17

- 18. IQ Test! What is the mode of operation of the SR flip-flop (set, reset or hold)? What is the output at Q from the SR flip-flop (active LOW inputs)? L ? High H Mode of operation = Set ? H ? High H Mode of operation = Hold ? H ? Low L Mode of operation = ? Reset 18

- 19. Clock SR Flip-Flop 4 Identify various types of flip-flops. 5 Build SR, JK, T and D flip – flop using logic gates. 6 Draw the symbol and truth table of SR, JK, T and D flip – flop. 19

- 20. Clock • Flip-flops: synchronous bistable devices • Output changes state at a specified point on a triggering input called the clock. • Change state either at the positive edge (rising edge) or at the negative edge (falling edge) of the clock signal. Clock signal Positive Negative edges edges 20

- 21. Clock SR Flip-Flop • The Clocked SR Flip Flop like SR flip-flop but with extra third input of a standard clock pulse. • The output of Q and NOT Q will not change (despite making changes to the inputs Set & Reset) in a Clocked RS Flip-flop Until receiving a signal from the clock. 21

- 22. Clock SR Flip-Flop Symbol: Clock SR Flip-flop (+ve EDGE) Clock SR Flip-flop (+ve EDGE) Combination gate Symbol 22

- 23. S Q Pulse CLK transition detector Q' R CLK' CLK' CLK CLK* CLK CLK* CLK CLK CLK' CLK' CLK* CLK* Positive-going transition Negative-going transition (rising edge) (falling edge) 23

- 24. Clock SR Flip-Flop Truth Table: • S-R flip-flop: on the triggering edge of the clock pulse, • S=HIGH and R=LOW is a SET state • R=HIGH (and S=LOW) is a RESET state • If both SR inputs LOW a NO change • If both SR inputs HIGH a INVALID • Truth table of positive edge-triggered S-R flip-flop: S R CLK Q(t+1) Comments X = irrelevant (“don’t care”) 0 0 X Q(t) No change = clock transition LOW to HIGH 0 1 0 Reset 1 0 1 Set 1 1 ? Invalid 24

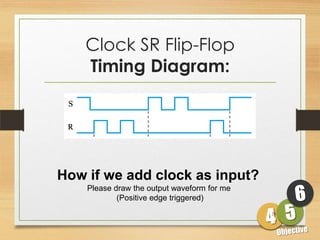

- 25. Clock SR Flip-Flop Timing Diagram: How if we add clock as input? Please draw the output waveform for me (Positive edge triggered) 25

- 26. D Flip-Flop 4 Identify various types of flip-flops. 5 Build SR, JK, T and D flip – flop using logic gates. 6 Draw the symbol and truth table of SR, JK, T and D flip – flop. 26

- 27. D Flip-Flop D Q Truth Table: C Q' • D flip-flop: single input D (data) • D=HIGH a SET state • D=LOW a RESET state • Q follows D at the clock edge. • D flip-flop formed by add NOT gate between SR input. D S Q D CLK Q(t+1) Comments CLK C 1 1 Set R Q' 0 0 Reset = clock transition LOW to HIGH 27

- 28. D Flip-Flop Symbol: D Q CLK Q' D Flip-flop (+ve EDGE) D Flip-flop (+ve EDGE) Combination gate Symbol 28

- 29. D Flip-Flop Timing Diagram: CLK CLK CLK CLK Q Q’ 29

- 30. JK Flip-Flop 4 Identify various types of flip-flops. 5 Build SR, JK, T and D flip – flop using logic gates. 6 Draw the symbol and truth table of SR, JK, T and D flip – flop. 30

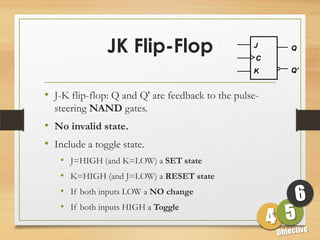

- 31. JK Flip-Flop J C Q K Q' • J-K flip-flop: Q and Q' are feedback to the pulse- steering NAND gates. • No invalid state. • Include a toggle state. • J=HIGH (and K=LOW) a SET state • K=HIGH (and J=LOW) a RESET state • If both inputs LOW a NO change • If both inputs HIGH a Toggle 31

- 32. JK Flip-Flop Symbol: J Q CLK Q' K JK Flip-flop (+ve EDGE) JK Flip-flop (+ve EDGE) Combination gate Symbol 32

- 33. JK Flip-Flop Truth Table: J K CLK Q(t+1) Comments 0 0 Q(t) No change 0 1 0 Reset 1 0 1 Set 1 1 Q(t)' Toggle 33

- 34. JK Flip-Flop Application: Frequency Division High High High J J QA J QB Q CLK C CLK C C K K K CLK CLK Q QA QB Divide clock frequency by 2. Divide clock frequency by 4. 34

- 35. JK Flip-Flop Timing Diagram: Similar to S-R flip-flop but toggles when J = K = 1 35

- 36. T Flip-Flop 4 Identify various types of flip-flops. 5 Build SR, JK, T and D flip – flop using logic gates. 6 Draw the symbol and truth table of SR, JK, T and D flip – flop. 36

- 37. T Flip-Flop T J Q Truth Table: CLK C K Q' • T flip-flop: single-input version of the J-K flip flop, formed by tying both inputs together. T T CLK Q(t+1) Comments Q 0 Q(t) No change CLK 1 Q(t)' Toggle Q' 37