A Systematic Approach to Creating Behavioral Models (CDNLive Slides)

- 1. A Systematic Approach to Creating Behavioral Models CDNLive, March, 2015 Bob Peruzzi, Joe Medero

- 2. Agenda • Introduction – Mixed-Signal Systems on Chips – Link to White Paper – Model accuracy and trade-offs – Good and bad models • Creating Models – Keep Cell Views Sync’d – Top-Down with SMG – Learn the Circuit – Plan the Model – Write the Model Code • Validating Models – Accurate versus plan? – Detects errors? – Test benches – Collaborative Effort • Maintaining Models Through Project Lifetime – AMS Design and Model Validator • Models and Applications – Analog Models – Digital Models – Real Number Models • Verification – Digital Verification with RNM – Analog Verification with RNM – Common Verification Platform – Common Verification Overview • Summary 2

- 4. • It’s a mixed-signal SOC world out there. Why all this integration into bigger and more complicated mixed-signal SOCs? Because it makes financial sense. • Evolution or extinction • Survive by embracing the inevitable – Independent digital, independent analog, and closely-coupled analog and digital subsystems coexist on the same die – Verification of the full chip must be done from the top level – SPICE type electrical simulators cannot simulate the full chip – Behavioral models must be used – Mixed signal verification must follow the lead of UVM or similar digital approaches – Digital verification methodologies must adapt to include analog • Our talk is about creating behavioral models Introduction – Mixed-Signal Systems on Chips 4

- 5. For the white paper “A Systematic Approach to Creating Behavioral Models” accompanying this presentation, follow this link: http://tinyurl.com/Xtreme-EDA-Customer-Resources A Systematic Approach to Creating Behavioral Models Introduction – Link to White Paper 5

- 6. • Cadence Lava Lamp – Accuracy versus Performance – http://community.cadence.com/CSSharedFiles/blogs/ms/2012/BS_Sim_Performance.jpg Introduction – Model accuracy and trade-offs 6

- 7. • What about behavioral models? – Model writer bridges the gap between analog design and digital verification – Model writer knows the analog behavior and knows how to target toward UVM • “A Bad Model is Worse than No Model“ – When model ignores faulty inputs – Incorrect behavior • Our approach to creating, validating and maintaining good models is what this presentation is all about Introduction – Good and bad models 7

- 8. • Open a schematic view of the block to be modeled • Use “create Verilog-AMS” to automatically create the shell of a Verilog-AMS model, with I/O matching the schematic Creating Models – Keep Cell Views Sync’d 8 Schematic Symbol Verilog-AMS

- 9. • Top-Down Approach: Designer works to match the model. • SMG is a good way to create the initial model for the designer to match Creating Models – Top Down with SMG 9 Graphical model is simulate-able, and may be compiled into Verilog- AMS (electrical or wreal) or System Verilog with real signals.

- 10. • Study the schematic • Interview its designer • Develop a description of the circuit behavior. Narrative text, equations, tables, sketches of diagrams and waveforms • Comment the description into the model file. If you use nedit, ASCII drawing is nearly as easy as Power Point. Creating Models – Learn the Circuit 10

- 11. • The designer blesses the description • Henceforth, the designer is obligated to notify the model's owner of any changes to pinout or functional behavior • The model owner is obligated to update the description as well as the model Creating Models – Learn the Circuit 11

- 12. • Decide what to include and what to leave out from the model – Collaboration between stake holders – Model Designer is the bridge between Circuit Designer and Verification Lead • Verification plan drives the models • Some behaviors which may be left out of the model – Bandwidth of a fixed-bandwidth amplifier, unless required by V-plan – Digitally programmable bandwidth, for most testcases – Sensitivity to magnitude of VDD, VREF, IBIAS. (Just check they’re within bounds.) Creating Models – Plan the Model Views 12

- 13. Creating Models – Plan the Model Views PLL Realistic Model • Program selection of capacitance • Program frequency dividers M, N, N-fraction • Oscillator spin-up from runt pulses. May require an injected “kick” • Control loop – Frequency, phase acquisition – Lock – Recovery from disturbances – Phase jitter • Frequency set-point changes – Re-programming – Same control loop Dedicated Verilog-AMS testbench • Low levels may be transistor level • Characterize worst-case delays Full chip testbench • Maybe 2 testcases need this much detail PLL RNM • Program selection of capacitance • Program frequency dividers M, N, N-fraction • Wait for characterized worst case delay – Output ideal clock – Optionally inject disturbance – Optionally inject phase jitter • Frequency set-point changes – Re-programming – For the characterized delay, ramp frequency transient Full chip testbench • Nearly every testcase 13

- 14. Creating Models – Plan the Model Views AFE Path Startup Transient Realistically Modeled • Transient response up to the A/D input • Static DC step without any AC applied • Is this detail necessary? – Maybe for some testcases – Mostly not AFE Path Startup Transient RNM Modeled • Wait and step • Key behavior is the wait-time • With RNM the step will not cause a loss of simulation convergence. • Is this good enough? – Depends on the V-Plan 14

- 15. Creating Models – Plan the Model Views AFE Realistic Models • Needed for front end verification – Analog signal flow – Digital Control – Calibration, Compensation – Adaptation (feedback) AFE Model for Digital Stimulus • For verifying downstream digital • Provides zero AFE coverage • Is this okay? – Depends on the V-Plan 15 Pre-amp VGA CTF A/D DSP CLK Stimulus (analog) AFE DSP CLKStimulus (digital) AFE A FE AFE

- 16. • The lead verification engineer and circuit designer bless the plan. • Comment the plan into the model description. – Archive the model with description, and always revise the description if you change the model Creating Models – Plan the Model Views 16

- 17. • Write the model to fit its description. – This is the easy part. • Validating the model is the toughest part. Creating Models – Write the Model Code 17

- 18. • Validation answers two questions: – Does the model match the model plan? – Does the model respond correctly to all input scenarios, including illegal combinations and bad logic? • Validation testbench – Separate from full chip testbench – Testbench schematic connects symbols for the (DUT) and driver-monitor (DMON). – Sometimes it makes sense to build up a validation testbench for more than one cell Validating Models – Accurate versus plan 18

- 19. • Validation ought to be independent and disinterested, but it seldom turns out that way. • Circuit designer would be a likely candidate to validate the model, but may not know the modeling language or the intricacies and pitfalls of the AMS simulator • Our approach to validation, beginning with testbench Validating Models – Test Benches 19

- 20. • Does the model match the model plan? 1. Circuit and model designers collaborate to describe analog and digital stimulus 2. Model designer creates DMON stimulus 3. Simulates schematic and model. 4. Debugs until they “match” 5. Delivers a turnkey simulation scenario to circuit designer 6. Circuit designer reruns simulation in a familiar environment 7. Circuit designer “blesses” model and stimulus Validating Models – Collaborative Effort 20

- 21. • Does the model respond correctly to all input scenarios, including illegal combinations and bad logic? 1. Use constrained random approach where possible 2. Include out-of-range analog 3. Include illegal combinations of logic 4. Include unknown ‘x’ states 5. Want to ensure the model doesn’t “pretend” everything is okay Validating Models 21

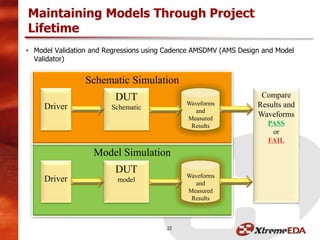

- 22. • Model Validation and Regressions using Cadence AMSDMV (AMS Design and Model Validator) Maintaining Models Through Project Lifetime 22 Model Simulation Schematic Simulation Driver DUT Schematic Waveforms and Measured Results Driver DUT model Waveforms and Measured Results Compare Results and Waveforms PASS or FAIL

- 23. • DUT: CML Buffer • DMON – Generates the power supplies and bias current – Drives the differential input signals to the DUT Virtuoso Testbench 23

- 24. • The configuration file used is to show differences with the AMS configuration files. Configuration and ADE State for Spectre 24

- 25. Configuration and ADE State for AMS 25 Needed for Wreal Leave blank for Pure Verilog

- 26. • Option: -define XEDA_USE_REAL – When defined uses Wreal • `XEDA_WREAL = wreal – When not it is a digital model • `XEDA_WREAL = “” CML BUF Dual Path Model (RNM or Verilog) 26

- 27. ADE XL Simulation Environment 27

- 29. AMSDMV Setup 29 Press the green button to run sims Simulation complete message Reference Simulation Compare Simulation

- 30. AMSDMV Failed to Match Case • Absolute Tolerance Set to 100mV • Failure Reports 30

- 31. AMSDMV Pass • Absolute Tolerance Set to 200mV • Alternatively, we could have set the E2R connect module to provide better accuracy. • No Error Points Shown 31

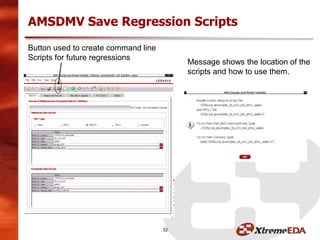

- 32. AMSDMV Save Regression Scripts 32 Button used to create command line Scripts for future regressions Message shows the location of the scripts and how to use them. Reference Simulation

- 33. • Analog Verification Models – System Level/Architecture Models • VerilogA, VerilogAMS, analog library components, SMG Library • Proof of concept – schematics/topologies not completely defined • Determining specifications for each block • Example: ADC, … – Analog Mixed Signal Models • VerilogA, Verilog AMS, VHDL AMS, Verilog/VHDL, etc. • Provides simulation speedup – Top level simulations are able to run in reasonable time. – Individual blocks can be tested thoroughly – When including the digital blocks it provides valuable feedback between analog and digital interface functionality and performance. – Example: Test bench for a frequency synthesizer • Cadence SMG (Schematic Model Generator) allows automatic generation of these types of models. Models and Applications 33

- 34. • Digital Verification Models – Verilog, VHDL, System Verilog, System C, … – High Level representation of the Analog block • Normally written early by the digital team • Does not include the full Analog functionality • Interconnectivity and hierarchical differences can be prevalent • Dynamic changes to analog blocks and functionality is not tracked. • Specifications may not be up to date and therefore lagging the design. • Metrics are not indicative of overall project status – They can give the RTL and verification teams a false sense of design completeness and coverage that is not present if the full analog system/model is included. Models and Applications 34

- 35. • Real Number Models (RNM) – Wreal, System Verilog, … – Use in Analog, Digital, and Mixed-Signal environments • Virtuoso, Incisive (irun) with directed and UVM tests. – Allows for tests to be shared between Analog and Digital Environments. – Allows for complete system verification • Code Coverage • Assertions (Formal, Simulation) • Functional Coverage • Constrained Random Simulation • Power Aware Design and Verification – CPF/UPF, multi-power domain analysis, isolation, in-rush current, level- shifting, state initialization, state retention, clock-gating, reset, power and current distribution, Power-State Machine verification. Models and Applications 35

- 36. • The code is written to provide a pure digital path or a wreal path. – Digital path used by the digital verification team without impact on simulation performance. – Wreal used by Analog team or selected digital sims for functional coverage. • Wreal and digital path code is shared so code coverage metrics are the same. • XEDA_POWER_AWARE switch checks power if defined. • The XEDA_CHK_PWR macro is an example of checking power consistently and to clean up the main code. – Assertions can also be added to the macro if needed. Dual Path Model (RNM or Verilog) 36

- 37. • RNM allows now the Analog and Digital teams to perform verification on the individual platforms to verify the system quickly. • If an issue is found in the RNM models used by the digital verification team debugging time may take too long. – Digital teams have limited analog background and are not familiar with the circuits and operation. – Analog teams are unfamiliar with the verification environment and this limits the help they can provide. • The Analog Engineer then tries to create a test bench that mimics the issues found in the system verification. – Time consuming and no guarantee that the system is well simulated. • How do we solve these issues? – By providing a Common Verification Platform in the analog environment that uses the digital verification teams platform and tests to speed up test bring up time and to allow quick cooperation in debugging issues. RNM Verification 37

- 38. Common Verification Platform 38 Testbench UVC1 mondriver scoreboardUVC2 mondriver scoreboardUVCn mondriver scoreboard Sequencer Testbench schematic, veriloga verilogams, Stop View DUT Incisive SOC Verification Analog Verification DUT Version Controlled Schematic Spectre-AMS APS-AMS Spectre XPS MS AMS-Ultrasim AMS with RNM irun directed OVM UVM

- 39. Updating Analog Testbench for CVP 39

- 40. Configuration File 40 wreal used as stopping view: The netlister does not look inside the block. The model needs to be provided at run time. wreal is just a symbol.

- 41. Finding the instances • Use the AMS Options Menu to specify the manifest and command files to run. • $DM_DEMO_DIR is set with the project setup scripts. • The xeda_dm_demo.f is shown at the left. 41

- 42. ADE Simulation Netlist and Run Options • From ADE select the netlister and simulation engine. – In this case: • Netlister: OSS • Simulator: irun • Can select to run Batch or Interactive – Interactive selected to debug issues. 42

- 43. Digital Control from ADE AMS Simulation • In interactive mode – Have access to digital debug environment – Can load saved svcf files from the digital team to quickly load the signals and zoom on issues. 43

- 44. Using Virtuoso to trace signals 44 Virtuoso Visualization & Analysis Browser Can use Analog Tracer to select signals from the schematic

- 45. Using Simvision to trace signals 45 Simvision And/or can use Simvision to work with the digital verification team

- 46. • Specification and Verification driven designs – The hierarchy is built with the same structure and verification purpose. – Planning, Performance Metrics, Functional Coverage, Code Coverage, Assertions, Power Management is owned by all. • The top level (or block level) test bench can be instantiated in an Analog Schematic (Virtuoso). – A “stopping view” is selected when the digital TB is to be used. – The selection of tests, required files, etc are added to the AMS options form allowing the same “irun” command to run in Virtuoso. – Engineers don’t have to spend extra time generating the tests and familiarity with the debugging environments increases the efficiency of the team (self-checking methods can be used). CVP Highlights 46

- 47. • Taking separate verification efforts and direction • And bringing them together towards a common goal. CVP Goal 47

- 48. • Behavioral models must be accurate and targeted toward efficient design verification • There is no totally automatic way to create behavioral models, it is a collaborative effort between the circuit designer, the verification lead and the model writer • It is the collaborative nature of our procedure that increases the likelihood of error-free models, and error-free silicon When it comes to bridging the analog + UVM design verification gap, AMS, and digital verification, think XtremeEDA. With over 60 engineers in North America, we are a leading provider of expert front end design and verification engineering services. Summary 48