Data types and Operators Continued

- 1. VHDL 360© by: Mohamed Samy Samer El-Saadany

- 2. Copyrights Copyright © 2010/2011 to authors. All rights reserved • All content in this presentation, including charts, data, artwork and logos (from here on, "the Content"), is the property of Mohamed Samy and Samer El-Saadany or the corresponding owners, depending on the circumstances of publication, and is protected by national and international copyright laws. • Authors are not personally liable for your usage of the Content that entailed casual or indirect destruction of anything or actions entailed to information profit loss or other losses. • Users are granted to access, display, download and print portions of this presentation, solely for their own personal non-commercial use, provided that all proprietary notices are kept intact. • Product names and trademarks mentioned in this presentation belong to their respective owners. VHDL 360 © 2

- 3. Module 3 (Continued) Data Types and Operators

- 4. Objective • Introducing Data Types & Operators • Skills gained: – Familiarity with data types – More on Expressions & Operators – Modeling Memories VHDL 360 © 4

- 5. Outline • Expressions & Operators • Aggregate • Attributes VHDL 360 © 5

- 6. Operators • We have discussed some operators in Module 1* • Operators are subprograms defined for specific data type(s) – Operators of the standard types (eg. bit, integer,…) are defined in "STD" library; in "standard" package. This package is visible by default to all VHDL design units. Example 1: res <= (a and not(b)) or (not(a) and b); • Parentheses are used for readability and to control the association of operators and operands • Unless parentheses are used, the operators with the highest precedence are applied first *Module 1: Create your first model for a simple logic circuit VHDL 360 © 6

- 7. Operators Precedence • Operators’ precedence are in the following descending order: – Miscellaneous operators **, abs, not – Multiplication operators *, /, mod, rem – Sign operator +, - – Addition operators +, -, & – Shift operators sll, srl, sla, sra, rol, ror – Relational operators =, /=, <, <=, >, >=, ?=, ?/=, ?<, ?<=, ?>, ?>= – Logical operators and, or, nand, nor, xor, xnor – Condition operator ?? • Operators of the same precedence are applied from left to right Items in blue were added in VHDL 2008 VHDL 360 © 7

- 8. Logical Operators Operation Package Comments bit <= bit AND bit; Standard Similarly NAND, OR, NOR, bit_vector <= bit_vector AND bit_vector; XOR…etc std_logic <= std_logic AND std_logic; ieee.std_logic_1164 Similarly NAND, OR, NOR, std_logic_vector <= std_logic _vector AND std_logic_vector; XOR…etc std_logic_vector <= std_logic AND std_logic_vector; ieee.std_logic_1164 VHDL 2008 standard* Similarly NAND, OR, NOR, XOR…etc • When the operands are arrays they must have the same size • Operations on arrays are done starting from the left towards the right *Not yet supported by all tools in the market VHDL 360 © 8

- 9. Addition Operators Operation* Package Comments integer<= integer +/- integer Standard std_logic_vector <= std_logic_vector +/- integer ieee.std_logic_unsigned Unsigned addition/subtraction std_logic_vector <= std_logic_vector +/- std_logic_vector ieee.std_logic_signed Signed addition/subtraction std_logic_vector <= std_logic_vector +/- std_logic std_logic_vector <= std_logic_vector +/- natural ieee.numeric_std_unsigned VHDL 2008 standard* std_logic_vector <= std_logic_vector +/- std_logic_vector ieee.numeric_std_signed std_logic_vector <= std_logic_vector +/- std_logic std_logic_vector <= std_logic_vector & std_logic Standard Operands can be of different size, std_logic_vector <= std_logic & std_logic_vector result’s size will be the sum of both std_logic_vector <= std_logic_vector & std_logic_vector sizes Example 2: Example 3: -- A: 3 bits cin : in std_logic; -- B: 5 bits a, b : in std_logic_vector(7 downto 0); -- C: 8 bits cout : out std_logic; C <= B & A; y : out std_logic_vector(7 downto 0)); B A signal result : std_logic_vector(8 downto 0); & A <= B & C result <= ('0' & a) + ('0' & b) + cin; cout <= result (8); C y <= result (7 downto 0); B A *Addition operators are Commutative *Not yet supported by all tools in the market VHDL 360 © 9

- 10. Reference page Relational Operators Operator Description Operand Types Result Type = Equality any type but file type or protected type Boolean /= Inequality < Smaller than scalar or discrete array types Boolean <= Smaller than or equal > Greater than >= Greater than or equal ?= Matching equality (VHDL 2008)* bit or std_ulogic or any one-dimensional array same as operand ?/= Matching inequality (VHDL 2008) type whose element type is BIT or STD_ULOGIC type or the element Type of the operands ?< Matching ordering (VHDL 2008) BIT or same as operand ?<= STD_ULOGIC type ?> ?>= • Operations on arrays are done starting from the left towards the right • When comparing arrays; always ensure that the arrays are the same size • Notice the return type of the matching operators *Not yet supported by all tools in the market VHDL 360 © 10

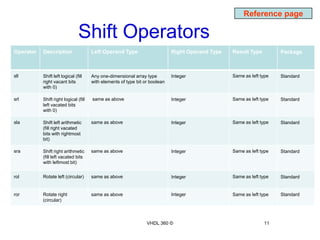

- 11. Reference page Shift Operators Operator Description Left Operand Type Right Operand Type Result Type Package sll Shift left logical (fill Any one-dimensional array type Integer Same as left type Standard right vacant bits with elements of type bit or boolean with 0) srl Shift right logical (fill same as above Integer Same as left type Standard left vacated bits with 0) sla Shift left arithmetic same as above Integer Same as left type Standard (fill right vacated bits with rightmost bit) sra Shift right arithmetic same as above Integer Same as left type Standard (fill left vacated bits with leftmost bit) rol Rotate left (circular) same as above Integer Same as left type Standard ror Rotate right same as above Integer Same as left type Standard (circular) VHDL 360 © 11

- 12. Reference page Shift Operators Operator Description Left Operand Type Right Operand Result Type Package Type SHL Shift left std_logic_vector std_logic_vector std_logic_vector ieee.std_logic_unsigned ieee.std_logic_signed SHR Shift right std_logic_vector std_logic_vector std_logic_vector ieee.std_logic_unsigned ieee.std_logic_signed sll Shift left logical std_logic_vector Integer std_logic_vector ieee.std_logic_1164* srl Shift right logical std_logic_vector Integer std_logic_vector ieee.std_logic_1164* rol Rotate left (circular) std_logic_vector Integer std_logic_vector ieee.std_logic_1164* ror Rotate right std_logic_vector Integer std_logic_vector ieee.std_logic_1164* (circular) * VHDL 2008, Not yet supported by all tools VHDL 360 © 12

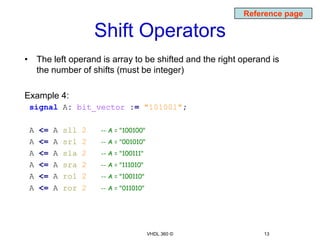

- 13. Reference page Shift Operators • The left operand is array to be shifted and the right operand is the number of shifts (must be integer) Example 4: signal A: bit_vector := "101001"; A <= A sll 2 -- A = "100100" A <= A srl 2 -- A = "001010" A <= A sla 2 -- A = "100111" A <= A sra 2 -- A = "111010" A <= A rol 2 -- A = "100110" A <= A ror 2 -- A = "011010" VHDL 360 © 13

- 14. Reference page Multiplication Operators Operator Description Left Operand Type Right Operand Type Result Type * Multiplication Any integer Same type Same type floating-point type Same type Same type / Division Any integer Same type Same type floating-point type Same type Same type mod Modulus Any integer type Same type Same type rem Remainder Any integer type Same type Same type VHDL 360 © 14

- 15. Reference page Multiplication Operators REM MOD Defined using the equation: Defined using the equation: A = (A/B)*B + (A rem B) A = B*N + (A mod B) Where: Where: A/B is an integer N is an integer (A rem B) has the same sign of A (A mod B) has the same sign of B Absolute value of (A rem B) < Absolute value of B Absolute value of (A mod B) < Absolute value of B Example 5 Example 6 5 rem 3 = 2 5 mod 3 = 2 (-5) rem 3 = -2 (-5) mod 3 = 1 (-5) rem (-3) = -2 (-5) mod (-3) = -2 5 rem (-3) = 2 5 mod (-3) = -1 11 rem 4 = 3 9 mod 4 = 1 (-11) rem 4 = -3 7 mod (-4) = -1 VHDL 360 © 15

- 16. Reference page Miscellaneous Operators Operator Description Left Operand Type Right Operand Result Type Type ** Exponentiation Integer type Integer type Same as left floating-point type Same as left abs Absolute value Any numeric type Same type not Logical negation Any bit or Boolean type Same type Example 7: x <= 5**5 -- ok y <= 0.5**3 -- ok x <= 4**0.5 -- illegal (the return type is not integer) y <= 0.5**(-2) -- ok Y <= 5**(-2) -- illegal (the return type is not integer) VHDL 360 © 16

- 17. Aggregate • Provides an easy way of assigning objects of composite types Example 8: Signal data_bus : std_logic_vector(15 downto 0); data_bus <= (15 downto 8 => '0' , others => '1'); --data_bus(1), data_bus(4), data_bus(7) are '1' while data_bus(2), data_bus(3) are '0';others are 'Z' data_bus <= (1 | 4 | 7 => '1', 2 | 3 => '0', others => 'Z'); data_bus <= (others => '1'); -- fill data_bus with ones data_bus <= ("0100", others => '1'); * -- data_bus <= "0100_1111_1111_1111" (carry_out, sum) <= ('0' & a) + ('0' & b); * -- target of an assignment data_bus <= B"0001_1111_0110_0000"; -- _ for readability data_bus <= X"1F05"; -- X stands for hexadecimal thus data_bus <= "0001_1111_0000_0101" * VHDL 2008 VHDL 360 © 17

- 18. Attributes (') • Attribute: a characteristic that something has – used to return information about a signal, variable or a data type – consists of an apostrophe “tick” mark (') followed by the attribute name • Predefined Type Attributes – 'left, 'right, 'low, 'high, 'image, … • Predefined Array Attributes – 'left, 'right, 'low, 'high, 'range, 'length, … • Predefined Signal Attributes – 'event, … VHDL 360 © 18

- 19. Attributes (') Example 9: ARCHITECTURE examp OF attrs IS Type myInt is range 0 to 15; Type states is (red, yellow, green); Type word is array (15 downto 0) of std_logic; Signal count: integer; signal mySig: myInt; signal state : states; BEGIN process begin mySig <= myInt'left; count <= word'left; state <= states'left; wait for 10 ns; mySig <= myInt'right; count <= word'right; state <= states'right; wait for 10 ns; mySig <= myInt'low; count <= word'low; state <= states'low; wait for 10 ns; mySig <= myInt'high; count <= word'high; state <= states'high; wait for 10 ns; count <= word'length; wait; end process; END ARCHITECTURE examp; VHDL 360 © 19

- 20. Example 10: Knight Rider LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY knight_rider IS port(clk, rst, enable: in std_logic; knight: out std_logic_vector(7 downto 0)); END ENTITY; ARCHITECTURE behave OF knight_rider IS signal temp: std_logic_vector(knight'range); signal count: integer range knight'low to knight'high; signal direction: std_logic; BEGIN process(clk) begin if rising_edge(clk) then if rst = '1' then temp <= (knight'left => '1', others => '0'); direction <= '1'; count <= 0; … VHDL 360 © 20

- 21. Knight Rider … elsif enable = '1' then if direction = '0' then temp <= temp(knight'left-1 downto knight'right) & temp (knight'left); else temp <= temp(knight'right) & temp(knight'left downto knight'right+1); end if; if count = knight'length-2 then count <= 0; direction <= not direction; else count <= count +1; end if; end if; end if; end process; knight <= temp; END ARCHITECTURE; VHDL 360 © 21

- 22. Contacts • You can contact us at: – http://www.embedded-tips.blogspot.com/ VHDL 360 © 22