DESIGN & ANALYSIS OF A CHARGE RE-CYCLE BASED NOVEL LPHS ADIABATIC LOGIC CIRCUITS FOR LOW POWER APPLICATIONS

- 1. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 DOI : 10.5121/vlsic.2012.3510 123 DESIGN & ANALYSIS OF A CHARGE RE-CYCLE BASED NOVEL LPHS ADIABATIC LOGIC CIRCUITS FOR LOW POWER APPLICATIONS Sanjeev Rai1 , Govind Krishna Pal2 , Ram Awadh Mishra3 and Sudarshan Tiwari4 1 Department of Electronics & Communication Engineering, Motilal Nehru National Institute of Technology, Allahabad, India [email protected] 2 Apache Design Solutions, Noida, India [email protected] 3 Department of Electronics & Communication Engineering, Motilal Nehru National Institute of Technology, Allahabad, India [email protected] 4 Director National Institute of Technology, Raipur, Chhatisgarh, India [email protected] ABSTRACT This paper focuses on principles of adiabatic logic, its classification and comparison of various adiabatic logic designs. An attempt has been made in this paper to modify 2PASCL (Two Phase Adiabatic Static CMOS Logic) adiabatic logic circuit to minimize delay of the different 2PASCL circuit designs. This modifications in the circuits leads to improvement of Power Delay Product (PDP) which is one of the figure of merit to optimize the circuit with factors like power dissipation and delay of the circuit. This paper investigates the design approaches of low power adiabatic gates in terms of energy dissipation and uses of Simple PN diode instead of MOS diode which reduces the effect of Capacitances at high transition and power clock frequency. A computer simulation using SPECTRE from Cadence is carried out on different adiabatic circuits, such as Inverter, NAND, NOR, XOR and 2:1 MUX. KEYWORDS Adiabatic logic, Low-power, Two phase clocked, Energy recovery, Split-level, Diode based logic, Power Delay Product (PDP), LPHS (Low Power High Speed). 1. INTRODUCTION The popularity of complementary MOS (CMOS) technology can be gauged from the fact that it has lower power consumption and high speed. However, the current trend towards ultra low- power has made researchers search for techniques to recycle energy from the circuits within. In conventional CMOS level-restoring logic, the switching event of circuits with rail-to-rail output voltage swing, causes an energy transfer from the power supply to the output node or from the output node to the ground. During a 0-to-VDD transition of the output, the total output charge Q = Cload VDD is drawn from the power supply at a constant voltage. Thus, an energy of E = CL VDD 2 is drawn from the power supply during this transition. Charging the output node capacitance to the voltage level VDD means that at the end of the transition, the amount of stored energy in the output node is E = ½ CL VDD 2 . Thus, half of the injected energy from the power supply is dissipated in the PMOS network while only one half is delivered to the output node. During a subsequent VDD-to-0 transition of the output node, no charge is drawn from the power supply and the energy stored in the load capacitance is dissipated in the NMOS network.

- 2. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 124 To reduce the dissipation, the circuit designer can minimize the switching events, decrease the node capacitance, reduce the voltage swing, or apply a combination of these methods. Yet in all these cases, the energy drawn from the power supply is used only once before being dissipated. To increase the energy efficiency of the logic circuits, other measures can be introduced for recycling the energy drawn from the power supply. A novel class of logic circuits called adiabatic logic [1],[2] offers the possibility of further reducing the energy dissipated during the switching events, and the possibility of recycling, or reusing, some of the energy drawn from the power supply. To accomplish this goal, the circuit topology and the operating principles have to be modified as per the need arises. The amount of energy recycling [3] achievable using adiabatic techniques is also determined by the process technology, switching speed, and the voltage swing. In conventional CMOS logic we use constant voltage source to charge the load capacitance but in case of adiabatic logic switching circuits we use constant current source instead of constant voltage source. Figure 1. depicts clearly how this can be achieved with subsequent explanation. Figure 1. Constant current source used for adiabatic logic circuit Dissipation in the switch = I2 *R Energy during charging E=( I2 *R)*T Also, The voltage across the switch = I*R Q=CL*Vdd , I = (CL *Vdd)/T (1.1) E=( I2 *R)*T = (R CL) / T * CL *Vdd2 (1.2) Where, E is the energy dissipated during charging time Q is the charge transferred to the load CL is the value of the load capacitance R is the on resistance of the PMOS switch VDD is the final value of the voltage at the load T is the charging time As explained above, the adiabatic switching power dissipation is asymptotically proportional to inverse of the charging time therefore, one can achieve very low energy dissipation [4] by slowing down the speed of operation and also the charge stored in the load capacitors can be recycled by using AC type power supply rather than DC. Now, couple of observations can be made based on Equation (1.2) as follows:

- 3. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 125 i. The energy dissipated for adiabatic circuits is smaller if the charging time T is larger than 2RCL. ii. Since, the dissipated energy is proportional to R thus reducing the on-resistance of the PMOS reduces the energy dissipation. Figure 2 shows the model of an adiabatic logic showing an ideal switch in series with resistance and two complementary voltage supply clocks. Figure 2. Model of adiabatic logic. In this paper, we propose a low-power high speed (LPHS) adiabatic logic circuit to achieve an optimized result between power dissipation and delay which significantly reduces PDP upto 40% when compared with 2PASCL logic circuit,also power consumption is compared with that of a conventional CMOS circuit. 2. PREVIOUS WORK Several adiabatic or Energy recovery logic architectures have been proposed over the years. They are based on the similar principle, but the structure and complexity, differ by, number of operation clock, Single- Dual rail style, Charging and discharging path etc. 2.1. Adiabatic logic structures are mainly of two types: Partially adiabatic logic. They are classified as – i) Efficient charge recovery logic (ECRL) ii) Quasi Adiabatic Logic(QAL) [5] iii) Positive feedback adiabatic logic (PFAL) iv) NMOS energy recovery logic v) True single phase adiabatic logic (TSAL) Fully adiabatic logic. They are classified as- i) Pass transistor adiabatic logic ii) 2 Phase adiabatic Static CMOS logic (2PASCL) iii) Split rail charge recovery logic (SCRL)

- 4. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 126 The previous work, using 2PASCL adiabatic logic shows that the power dissipation reduces by 60-70 % but delay of the circuit increases by as much as 30% as compared to the conventional CMOS circuit. These delays of the circuit occurred due to the MOS diode present in the discharging path of the circuit, because of the circuit operating at very high frequencies (10-100 MHz.) and at high frequency large number of capacitors are present which affects the time constant of the circuit. Time constant of the circuit increases due to charging and discharging of these capacitors at high power clock frequencies [6]. Therefore, delay of the circuit increases. 3. DESIGN APPROACHES AND PROPOSED CIRCUIT Before we discuss more about the proposed and 2PASCL circuit, let us discuss a Partially adiabatic logic circuit for e.g QAL (Quasi Adiabatic Logic). Figure 3 shows the schematic of Quasi adiabatic logic circuit design which can be extended to 4 Inverter chain. Figure 3. Quasi adiabatic logic. In the Quasi Adiabatic Logic circuit, the circuit components are driven by a sinusoidal supply power clock instead of a constant supply (DC supply) as used in Conventional CMOS circuit. The QAL inverter shown above in the schematic uses a power clock of sinusoidal supply, therefore, the power dissipation of the circuit improves 60-70%. Also the present paper discusses QAL using Pseudo nMOS, with MOS diode in charge recovery path. Due to these changes, we can save energy upto 15% as compared to conventional QAL. Both the schematic designs using Pseudo nMOS are shown below- Figure 4. Proposed inverter (Pseudo nMOS implemented with Adiabatic Logic)

- 5. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 A novel method for reducing delay in adiabatic circuit involves Simple PN diode instead of MOS dio At high frequencies of 10-100MHz, capacitances acting on MOS diode in 2PASCL charges and discharges at every power clock cycle which would effectiv circuit that leads to increases in digital design [7] it has always been the focus point of the engineers to keep the load capacitance under control so that the delay is under check. Figure 5. General diagram of LPHS Adiabatic logic circuit LPHS Adiabatic logic is similar to CMOS circuits except few changes which make this logic much more energy efficient than CMOS some other adiabatic logic circuits CMOS logic gate is the two diodes, one from the output node to the power clock supply and another one is placed next to the nMOS logic to another power clock. Both PN diodes are used to re-cycle the charges from the output node, to improve d This is especially advantageous for signal nodes with a long chain of switches The other difference is that split- replace the Vdd and the Vss. Substrate of pMOS is connected to Vø whereas for nMOS, it is connected to Vø bar. From the simulation, we found that split energy dissipation compared to trapezoidal power clock supply even if we set the T the trapezoidal waveforms to maximum values. By using two split where each peak-to-peak is 0.9 V, we can reduce the voltage difference, thus reducing the charging and discharging activities. Sinusoidal waveforms can also be energy efficiency than trapezoidal waveforms. The circuit operates in 2 phases – I. Evaluation phase: When the output node is LOW and pMOS tree is turned ON, Load capacitor is charged through pMOS transistor resulting in the HIGH state at the When the output is LOW and nMOS is ON, no transition occurs. The same result is obtained when the output node is HIGH and pMOS is ON. Finally, when HIGH and nMOS is ON, discharging via nMOS output voltage to Vt(threshold voltage) International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 A novel method for reducing delay in the Proposed circuit, Low Power High Speed (LPHS) adiabatic circuit involves Simple PN diode instead of MOS diode uses in 2PASCL logic circuit 100MHz, capacitances acting on MOS diode in 2PASCL charges and discharges at every power clock cycle which would effectively increase the capacitances of in the time constant resulting in increases of delay. For low power digital design [7] it has always been the focus point of the engineers to keep the load capacitance under control so that the delay is under check. . General diagram of LPHS Adiabatic logic circuit LPHS Adiabatic logic is similar to CMOS circuits except few changes which make this logic more energy efficient than CMOS with lesser delay as compared to 2PASCL as well as circuits also [8]. The notable difference between LPHS and static CMOS logic gate is the two diodes, one from the output node to the power clock supply and another one is placed next to the nMOS logic to another power clock. Both PN diodes are used to cycle the charges from the output node, to improve discharging speed of internal signal nodes. This is especially advantageous for signal nodes with a long chain of switches. -level sinusoidal power clock supplies, Vø and Vø bar are used to Substrate of pMOS is connected to Vø whereas for nMOS, it is connected to Vø bar. From the simulation, we found that split- level sinusoidal gives a lower energy dissipation compared to trapezoidal power clock supply even if we set the Trise the trapezoidal waveforms to maximum values. By using two split-level sinusoidal waveforms peak is 0.9 V, we can reduce the voltage difference, thus reducing the charging and discharging activities. Sinusoidal waveforms can also be generated with higher energy efficiency than trapezoidal waveforms. – hen the output node is LOW and pMOS tree is turned ON, Load capacitor is charged through pMOS transistor resulting in the HIGH state at the is LOW and nMOS is ON, no transition occurs. The same result is when the output node is HIGH and pMOS is ON. Finally, when output HIGH and nMOS is ON, discharging via nMOS takes place resulting in the decrease of (threshold voltage) value where the logical state is “0” [9 International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 127 Proposed circuit, Low Power High Speed (LPHS) de uses in 2PASCL logic circuit. 100MHz, capacitances acting on MOS diode in 2PASCL charges and capacitances of For low power digital design [7] it has always been the focus point of the engineers to keep the load capacitance LPHS Adiabatic logic is similar to CMOS circuits except few changes which make this logic 2PASCL as well as PHS and static CMOS logic gate is the two diodes, one from the output node to the power clock supply and another one is placed next to the nMOS logic to another power clock. Both PN diodes are used to ischarging speed of internal signal nodes. level sinusoidal power clock supplies, Vø and Vø bar are used to Substrate of pMOS is connected to Vø whereas for nMOS, it is level sinusoidal gives a lower rise and Tfall of level sinusoidal waveforms peak is 0.9 V, we can reduce the voltage difference, thus reducing the ated with higher hen the output node is LOW and pMOS tree is turned ON, Load capacitor is charged through pMOS transistor resulting in the HIGH state at the output. is LOW and nMOS is ON, no transition occurs. The same result is output node is resulting in the decrease of 9].

- 6. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 II. Hold phase: Now due to the diodes, the state of remains unchanged. When the preliminary state of the output node is HIGH, it will change to Vt, the threshold voltage of the diode. At this point, discharging via diode D1 occurs. From the operation of LPHS adiabatic logic as explained in dynamic switching are observed as circuit nodes are not necessarily every clock cycle which reduces the node switching activities significantly. Th lowers the switching activity lowering the 4. CIRCUIT SIMULATION Schematic design and simulation shown where comparison has been made for conventional CMOS and 2PASCL logic circuits with their power dissipation, delay and PDP. These results well conform for ul The simulation in this paper were performed using a SPECTRE circuit simulator with a 0.18 um, 1.8 V standard CMOS process. The width and Length of the nMOS and pMOS logic gates were 0.6 um and 0.18 um respectively. A load capacitance of 0.01 pF was connected to the output node. The frequency of the power supply clock was set to a value same as the transition frequency. In this era of digital integrated circuits [ degradation in the logic levels is the objective and the authors with the result have tried to prove this point. 4.1. Simulation Results The logic function of these fundamental logic are based on LPHS Adiabatic logic accordingly as shown in the corresponding tabulated. The time scale on the horizontal axis is in terms of nsecs. Th usual meaning. i. Schematic and Simulated waveforms of Vø Figure 6(a). Schematic and simulated waveform of LPHS Adiabatic International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 ue to the diodes, the state of output when preliminary state is LOW remains unchanged. When the preliminary state of the output node is HIGH, it will to Vt, the threshold voltage of the diode. At this point, discharging via diode D1 From the operation of LPHS adiabatic logic as explained in evaluation and hold dynamic switching are observed as circuit nodes are not necessarily charging and discharging every clock cycle which reduces the node switching activities significantly. This lowering the energy dissipation. IMULATION AND RESULTS and simulation results of INVERTER, NAND, NOR, XOR and 2:1 MUX where comparison has been made for a non cascaded gate to those design using conventional CMOS and 2PASCL logic circuits with their power dissipation, delay and PDP. These results well conform for ultra low power applications using these logic gates [9]. were performed using a SPECTRE circuit simulator with a 0.18 um, 1.8 V standard CMOS process. The width and Length of the nMOS and pMOS logic gates were m respectively. A load capacitance of 0.01 pF was connected to the output node. The frequency of the power supply clock was set to a value same as the transition In this era of digital integrated circuits [10] maintaining the logic level with le degradation in the logic levels is the objective and the authors with the result have tried to prove of these fundamental logic circuits which may form a basic cell for a design based on LPHS Adiabatic logic and has been observed that the circuits conform corresponding figures. The results have been categorized The time scale on the horizontal axis is in terms of nsecs. The other symbols have their Schematic and Simulated waveforms of different logic circuits Vout CL Schematic and simulated waveform of LPHS Adiabatic Inverter. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 128 when preliminary state is LOW remains unchanged. When the preliminary state of the output node is HIGH, it will to Vt, the threshold voltage of the diode. At this point, discharging via diode D1 hold phase, less charging and discharging on is significantly of INVERTER, NAND, NOR, XOR and 2:1 MUX are a non cascaded gate to those design using conventional CMOS and 2PASCL logic circuits with their power dissipation, delay and PDP. tra low power applications using these logic gates [9]. were performed using a SPECTRE circuit simulator with a 0.18 um, 1.8 V standard CMOS process. The width and Length of the nMOS and pMOS logic gates were m respectively. A load capacitance of 0.01 pF was connected to the output node. The frequency of the power supply clock was set to a value same as the transition ] maintaining the logic level with less degradation in the logic levels is the objective and the authors with the result have tried to prove circuits which may form a basic cell for a design conform to operate results have been categorized and well e other symbols have their Inverter.

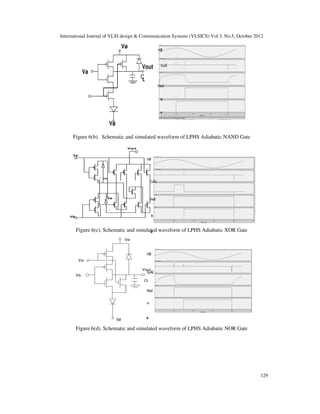

- 7. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 Vø Va Vø Figure 6(b). Schematic and simulated waveform of LPHS Adiabatic Vø Vø Va Vb Figure 6(c). Schematic and simulated waveform of LPHS Adiabatic V Vb Vø Va Figure 6(d). Schematic and simulated International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 ø CL Vout Schematic and simulated waveform of LPHS Adiabatic NAND Gate Vout Schematic and simulated waveform of LPHS Adiabatic XOR Gate Vø CL Vout Schematic and simulated waveform of LPHS Adiabatic NOR Gate International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 129 NAND Gate XOR Gate OR Gate

- 8. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 Vø S Vø A S B A S S B Figure 6(e).Schematic and simulated waveform of LPHS Adiabatic Figure 6(a) to 6(e) shows the simulated waveforms for the corresponding circuits of different gates where for each gate the current and output voltage has been shown for the applied inputs. The symbols shown in the figure have their usual meaning. i. Tables. Table 1 describes the power dissipation comparison of different logic gates for PD 2PASCL & PD-LPHS structures at 10fF capacitance and transition frequency of 25 MHz. Table 1.PD comparison at Designed Logic PD Inverter 7.1224 E NAND 7.12 E NOR 7.088 E XOR 7.782 E 2:1 MUX 7.244 E Table 2 describes the delay comparison of different logic gates for PD PD-LPHS structures at 10fF capacitance and transition frequency of 25 MHz. has also been used in the comparison of different structures. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 C B Vout Schematic and simulated waveform of LPHS Adiabatic 2:1 MUX Gate 6(a) to 6(e) shows the simulated waveforms for the corresponding circuits of different gates where for each gate the current and output voltage has been shown for the applied inputs. The symbols shown in the figure have their usual meaning. describes the power dissipation comparison of different logic gates for PD LPHS structures at 10fF capacitance and transition frequency of 25 MHz. PD comparison at CL= 10fF and transition frequency = 25 MHz PD- CMOS PD- 2PASCL PD- LPHS 7.1224 E-7 3.5568 E-7 3.5857 E-7 7.12 E-7 3.55 E-7 3.604 E-7 7.088 E-7 3.423 E-7 3.6631 E-7 7.782 E-7 1.88 E-7 2.135 E-7 7.244 E-7 2.412 E-7 2.614 E-7 comparison of different logic gates for PD-CMOS,PD LPHS structures at 10fF capacitance and transition frequency of 25 MHz. Note that 2:1 MUX has also been used in the comparison of different structures. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 130 2:1 MUX Gate 6(a) to 6(e) shows the simulated waveforms for the corresponding circuits of different gates where for each gate the current and output voltage has been shown for the applied inputs. describes the power dissipation comparison of different logic gates for PD-CMOS,PD- LPHS structures at 10fF capacitance and transition frequency of 25 MHz. 25 MHz CMOS,PD-2PASCL & Note that 2:1 MUX

- 9. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 131 Table 2. Delay comparison CL= 10fF and transition frequency =25 MHz Designed Logic CMOS Delay 2PASCL Delay LPHS Delay Inverter 5.7878 E-11 9.05454E11 3.302 E-11 NAND 3.254 E-11 4.665 E-11 1.928 E-11 NOR 1.4094 E-11 2.251 E-11 1.1587E-11 XOR 5.925 E-11 7.225 E-11 4.9842E-11 2:1 MUX 3.442 E-11 4.4572 E-9 3.29189E-9 Table 3 describes the power delay product of different logic gates for PD-CMOS,PD-2PASCL & PD-LPHS structures at 10fF capacitance and transition frequency of 25 MHz. Table 3.PDP comparison at CL= 10fF and transition frequency 25= MHz Designed Logic PDP -CMOS PDP -2PASCL PDP - LPHS Inverter 4.122 E-17 3.22 E-17 1.84 E-17 NAND 2.2897 E-17 1.224 E-17 0.695 E-17 NOR 9.122 E-17 6.872 E-17 4.244 E-17 XOR 1.064 E-16 8.232 E-16 6.325 E-16 2:1 MUX 13.38 E-16 11.64 E-16 8.62-16 iii. Figures:PD comparison between CMOS, 2PASCL and LPHS Adiabatic logic Figures 7 to Figure 10 shows the power dissipation comparison of CMOS, LPHS & 2PASCL structures at different output load capacitances which have been plotted for different logic gates.

- 10. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 Figure 7 Figure Figure 9 0 1 2 3 4 5 6 7 8 0 20 0 1 2 3 4 5 6 7 8 0 20 40 0 1 2 3 4 5 6 7 8 0 20 40 International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 Load Capacitance(fF) Figure 7. PD Versus CL Comparison(Inverter) Load Capacitance(fF) Figure 8. PD Versus CL Comparison(NAND) Load Capacitance (fF) Figure 9. PD Versus CL Comparison (NOR) 40 60 80 100 120 CMOS LPHS 2PASCL 40 60 80 100 120 CMOS 2PASCL LPHS 40 60 80 100 120 CMOS 2PASCL LPHS International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 132 CMOS LPHS 2PASCL CMOS 2PASCL LPHS CMOS 2PASCL LPHS

- 11. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 Figure iv. Figures: Four Inverter chain Figures 11 shows the power dissipation comparison of four inverter chain for CMOS, QAL, Pseudo NMOS QAL, Pseudo NMOS structures at different output load capacitances. Figure 12 shows the delay comparison for the mentioned structures at different loads and Figure 13 shows the Power Delay Product for the different structures at different load. verified using Cadence tool. Figure11 0 1 2 3 4 5 6 7 8 0 20 40 0 1 2 3 4 5 6 7 8 0 20 40 International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 Load Capacitance (fF) Figure 10. PD Versus CL Comparison (XOR) Inverter chain Comparisons. Figures 11 shows the power dissipation comparison of four inverter chain for CMOS, QAL, Pseudo NMOS QAL, Pseudo NMOS structures at different output load capacitances. Figure 12 the delay comparison for the mentioned structures at different loads and Figure 13 shows the Power Delay Product for the different structures at different load. The results have been Load Capacitance (fF) Figure11. PD(µw) Versus CL Comparison 40 60 80 100 120 CMOS 2PASCL LPHS 40 60 80 100 120 QAL Pseudo nmos QAL Pseudo nmos CMOS International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 133 Figures 11 shows the power dissipation comparison of four inverter chain for CMOS, QAL, Pseudo NMOS QAL, Pseudo NMOS structures at different output load capacitances. Figure 12 the delay comparison for the mentioned structures at different loads and Figure 13 shows The results have been CMOS 2PASCL LPHS Pseudo nmos QAL Pseudo nmos

- 12. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 134 Load Capacitance (fF) Figure 12. Delay (ns) Versus CL comparison Load Capacitance (fF) Figure 13. PDP Versus CL comparison The functionality of the proposed circuit with variation in different parameters (like load capacitance, frequency and voltage) has been examined. Using proposed adiabatic logic [11], we can reduce delay upto 40% compared with the 2PASCL. LPHS reduces delay at the cost of power dissipation and output swing of the circuit. Output swing reduces from 0.5-1.8 to 0.7-1.8. Further, it is important to note that the clock plays a very important role for these type of digital circuits not because charge recycling has been employed but due the dependence power consumption on it, there whether single phase clock is being used on two phase it is utmost important to control the clock [11-14]. 5. CONCLUSION This paper primarily focuses on the design of low power high speed CMOS cell structures. A family of full-custom conventional CMOS Logic and an Adiabatic Logic units were designed in Cadence Design Architect using standard TSMC 0.18 µm technology and further the analysis of 0 0.2 0.4 0.6 0.8 1 1.2 0 50 100 150 CMOS QAL Pseudo nmos QAL Pseudo nmos with diode adiabatic 0 1 2 3 4 5 6 7 0 50 100 150 QAL Pseudo nmos QAL Pseudo nmos with diode CMOS

- 13. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 135 the average dynamic power dissipation and delay with respect to the load capacitance was done. It was found that the Proposed adiabatic logic style is advantageous in applications where power reduction as well as speed is of prime importance as in high performance battery-portable digital systems running on batteries such as note-book computers, cellular phones, personal digital assistants, etc. We have achieved an improvement of 60 to 70% in power consumption as compared with Conventional CMOS circuits. This reduction in power consumption is achieved by adiabatic logic with split level power supply. The comparison of the 2PASCL circuit with Conventional CMOS has proved that power consumption with 2PASCL logic is far less as compared to CMOS based technique but delay increases. Delay comparatively increases in 2PASCL but using modified logic we can optimize the circuit between delay, power and output swing. ACKNOWLEDGEMENTS The authors duly acknowledged with gratitude the support from ministry of communication and information technology, DIT Govt. of India, New Delhi, through special manpower Development program in VLSI and related Software’s Phase-II (SMDP-II) project in ECE Department, MNNIT Allahabad-211004, India. REFERENCES [1] N. Anuar, Y. Takahashi and T. Sekine, “Two phase clocked adiabatic static CMOS logic and its Logic Family,” Joural of Semiconductor Technology & Science. Vol.10 No.1, Mar. 2010. [2] N. Anuar, Y. Takahashi and T. Sekine, “Two phase clocked adiabatic static logic circuit: a proposal for digital low power applications,” Proc. IEICE Gen. Conf., p.102, Mar. 2009. [3] T. Indermauer and M. Horowitz, “Evaluation of Charge Recovery Circuits and Adiabatic Switching for Low Power Design,” Technical Digest IEEE Symposium Low Power Electronics, San Diego, pp. 102-103, October 2002. [4] W. C. Athas, J. G. Koller, L. Svensson, “An Energy- Efficient CMOS Line Driver using Adiabatic Switching,” Fourth Great Lakes symposium on VLSI, California, March 2005. [5] Y. Ye, and K. Roy, “QSERL: Quasi-static energy recovery logic,” Solid-States Circuits., IEEE Journal, Vol.36, Issue 2, Feb., 2001, pp. 239-248. [6] N. Waste and K. Eshraghian, Principle of CMOS VLSI Design: A System Prospective, 2nd ed. New York: Addison – Wesley, 1993. [7] A. P. Chandrakashan, S. Sheng, and R. W. Brodersen, “Low Power CMOS Digital Design,” IEEE Journal of Solid-state Circuits, Vol. 27, No. 04, pp. 473-484, April 1999. [8] W.C.Athes, L.J. Svensson, J.G. Koller, et al., “Low-power digital systems based on adiabatic- switching principles,” IEEE Trans. On VLSI Systems, 2(4): 398-407, December 1994. [9] A.Blotti and R. Saletti, “Ultralow- Power Adiabatic Circuit Semi-Custom Design,” IEEE Transactions on VLSI Systems, vol. 12, no. 11, pp. 1248-1253, November 2004. [10] Sung Mo Kang and Yusuf Leblebici, CMOS Digital Integrated Circuits - Analysis and Design, McGraw-Hill, 2003. [11] S. Samantha “Adiabatic computing: A Contemporary Review,” International conference on computers and devices for communication, Dec. 2009, pp.1-4 [12] J. Marjonen and M Aberg, “A single clocked adiabatic static logic – a proposal for digital low power application,” J. VLSI signal processing, vol.27, no. 27, Feb.2001, pp.253-268. [13] B.Voss and M. Glesner, “A Low Power Sinusoidal Clock,” In Proc. of the International Symposium on Circuits and Systems, ISCAS 2001. [14] Y. Moon and D. K. Jeong, “An Efficient Charge Recovery Logic Circuit,” IEEE JSSC, Vol. 31, No. 04, pp. 514-522, April 1996.

- 14. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012 136 Authors Short Biography Mr. Sanjeev Rai – Was born on 21st July 73 in a remote village of District Ballia, State Uttar Pradesh, India and completed graduation from Government Engineering College, Raipur, now known as NIT Raipur, did Masters in Digital Systems from Motilal Nehru Regional Engineering College, Allahabad, now known as MNNIT, Allahabad. Presently serving as Assistant Professor in the Department of Electronics & Communication Engineering, MNNIT Allahabad, India. Primarily the research interest includes Microelectronics & VLSI Design & Semiconductor Device Modeling. Mr. Govind Krishna Pal – is currently working with Apache Design Solutions as Application Engineer his area of interest is VLSI Design and its applications Dr. Ram Awadh Mishra – Currently working as Associate Professor in the Department of Electronics & Communication Engineering, MNNIT Allahabad, India. Primarily the research interest includes Semiconductor Device Modeling. Dr.Sudarshan Tiwari – Is currently working as Director, NIT Raipur, Chattisgarh. He has formerly worked as Professor & Head Department of Electronics & Communication Engineering, MNNIT Allahabad, India. Primarily the research interest includes Microelectronics & Optical Communication.

![International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012

124

To reduce the dissipation, the circuit designer can minimize the switching events, decrease the

node capacitance, reduce the voltage swing, or apply a combination of these methods. Yet in all

these cases, the energy drawn from the power supply is used only once before being dissipated.

To increase the energy efficiency of the logic circuits, other measures can be introduced for

recycling the energy drawn from the power supply. A novel class of logic circuits called adiabatic

logic [1],[2] offers the possibility of further reducing the energy dissipated during the switching

events, and the possibility of recycling, or reusing, some of the energy drawn from the power

supply. To accomplish this goal, the circuit topology and the operating principles have to be

modified as per the need arises. The amount of energy recycling [3] achievable using adiabatic

techniques is also determined by the process technology, switching speed, and the voltage swing.

In conventional CMOS logic we use constant voltage source to charge the load capacitance but in

case of adiabatic logic switching circuits we use constant current source instead of constant

voltage source. Figure 1. depicts clearly how this can be achieved with subsequent explanation.

Figure 1. Constant current source used for adiabatic logic circuit

Dissipation in the switch = I2

*R

Energy during charging E=( I2

*R)*T

Also,

The voltage across the switch = I*R

Q=CL*Vdd , I = (CL *Vdd)/T (1.1)

E=( I2

*R)*T = (R CL) / T * CL *Vdd2

(1.2)

Where,

E is the energy dissipated during charging time

Q is the charge transferred to the load

CL is the value of the load capacitance

R is the on resistance of the PMOS switch

VDD is the final value of the voltage at the load

T is the charging time

As explained above, the adiabatic switching power dissipation is asymptotically proportional to

inverse of the charging time therefore, one can achieve very low energy dissipation [4] by

slowing down the speed of operation and also the charge stored in the load capacitors can be

recycled by using AC type power supply rather than DC.

Now, couple of observations can be made based on Equation (1.2) as follows:](https://image.slidesharecdn.com/3512vlsics10-190316120800/85/DESIGN-ANALYSIS-OF-A-CHARGE-RE-CYCLE-BASED-NOVEL-LPHS-ADIABATIC-LOGIC-CIRCUITS-FOR-LOW-POWER-APPLICATIONS-2-320.jpg)

![International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012

125

i. The energy dissipated for adiabatic circuits is smaller if the charging time T is

larger than 2RCL.

ii. Since, the dissipated energy is proportional to R thus reducing the on-resistance

of the PMOS reduces the energy dissipation.

Figure 2 shows the model of an adiabatic logic showing an ideal switch in series with resistance

and two complementary voltage supply clocks.

Figure 2. Model of adiabatic logic.

In this paper, we propose a low-power high speed (LPHS) adiabatic logic circuit to achieve an

optimized result between power dissipation and delay which significantly reduces PDP upto 40%

when compared with 2PASCL logic circuit,also power consumption is compared with that of a

conventional CMOS circuit.

2. PREVIOUS WORK

Several adiabatic or Energy recovery logic architectures have been proposed over the years. They

are based on the similar principle, but the structure and complexity, differ by, number of

operation clock, Single- Dual rail style, Charging and discharging path etc.

2.1. Adiabatic logic structures are mainly of two types:

Partially adiabatic logic. They are classified as –

i) Efficient charge recovery logic (ECRL)

ii) Quasi Adiabatic Logic(QAL) [5]

iii) Positive feedback adiabatic logic (PFAL)

iv) NMOS energy recovery logic

v) True single phase adiabatic logic (TSAL)

Fully adiabatic logic. They are classified as-

i) Pass transistor adiabatic logic

ii) 2 Phase adiabatic Static CMOS logic (2PASCL)

iii) Split rail charge recovery logic (SCRL)](https://image.slidesharecdn.com/3512vlsics10-190316120800/85/DESIGN-ANALYSIS-OF-A-CHARGE-RE-CYCLE-BASED-NOVEL-LPHS-ADIABATIC-LOGIC-CIRCUITS-FOR-LOW-POWER-APPLICATIONS-3-320.jpg)

![International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012

126

The previous work, using 2PASCL adiabatic logic shows that the power dissipation reduces by

60-70 % but delay of the circuit increases by as much as 30% as compared to the conventional

CMOS circuit. These delays of the circuit occurred due to the MOS diode present in the

discharging path of the circuit, because of the circuit operating at very high frequencies (10-100

MHz.) and at high frequency large number of capacitors are present which affects the time

constant of the circuit. Time constant of the circuit increases due to charging and discharging of

these capacitors at high power clock frequencies [6]. Therefore, delay of the circuit increases.

3. DESIGN APPROACHES AND PROPOSED CIRCUIT

Before we discuss more about the proposed and 2PASCL circuit, let us discuss a Partially

adiabatic logic circuit for e.g QAL (Quasi Adiabatic Logic). Figure 3 shows the schematic of

Quasi adiabatic logic circuit design which can be extended to 4 Inverter chain.

Figure 3. Quasi adiabatic logic.

In the Quasi Adiabatic Logic circuit, the circuit components are driven by a sinusoidal supply

power clock instead of a constant supply (DC supply) as used in Conventional CMOS circuit. The

QAL inverter shown above in the schematic uses a power clock of sinusoidal supply, therefore,

the power dissipation of the circuit improves 60-70%.

Also the present paper discusses QAL using Pseudo nMOS, with MOS diode in charge recovery

path. Due to these changes, we can save energy upto 15% as compared to conventional QAL.

Both the schematic designs using Pseudo nMOS are shown below-

Figure 4. Proposed inverter (Pseudo nMOS implemented with Adiabatic Logic)](https://image.slidesharecdn.com/3512vlsics10-190316120800/85/DESIGN-ANALYSIS-OF-A-CHARGE-RE-CYCLE-BASED-NOVEL-LPHS-ADIABATIC-LOGIC-CIRCUITS-FOR-LOW-POWER-APPLICATIONS-4-320.jpg)

![International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012

A novel method for reducing delay in

adiabatic circuit involves Simple PN diode instead of MOS dio

At high frequencies of 10-100MHz, capacitances acting on MOS diode in 2PASCL charges and

discharges at every power clock cycle which would effectiv

circuit that leads to increases in

digital design [7] it has always been the focus point of the engineers to keep the load capacitance

under control so that the delay is under check.

Figure 5. General diagram of LPHS Adiabatic logic circuit

LPHS Adiabatic logic is similar to CMOS circuits except few changes which make this logic

much more energy efficient than CMOS

some other adiabatic logic circuits

CMOS logic gate is the two diodes, one from the output node to the power clock supply and

another one is placed next to the nMOS logic to another power clock. Both PN diodes are used to

re-cycle the charges from the output node, to improve d

This is especially advantageous for signal nodes with a long chain of switches

The other difference is that split-

replace the Vdd and the Vss. Substrate of pMOS is connected to Vø whereas for nMOS, it is

connected to Vø bar. From the simulation, we found that split

energy dissipation compared to trapezoidal power clock supply even if we set the T

the trapezoidal waveforms to maximum values. By using two split

where each peak-to-peak is 0.9 V, we can reduce the voltage difference, thus reducing the

charging and discharging activities. Sinusoidal waveforms can also be

energy efficiency than trapezoidal waveforms.

The circuit operates in 2 phases –

I. Evaluation phase: When the output node is LOW and pMOS tree is turned ON, Load

capacitor is charged through pMOS transistor resulting in the HIGH state at the

When the output is LOW and nMOS is ON, no transition occurs. The same result is

obtained when the output node is HIGH and pMOS is ON. Finally, when

HIGH and nMOS is ON, discharging via nMOS

output voltage to Vt(threshold voltage)

International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012

A novel method for reducing delay in the Proposed circuit, Low Power High Speed (LPHS)

adiabatic circuit involves Simple PN diode instead of MOS diode uses in 2PASCL logic circuit

100MHz, capacitances acting on MOS diode in 2PASCL charges and

discharges at every power clock cycle which would effectively increase the capacitances of

in the time constant resulting in increases of delay. For low power

digital design [7] it has always been the focus point of the engineers to keep the load capacitance

under control so that the delay is under check.

. General diagram of LPHS Adiabatic logic circuit

LPHS Adiabatic logic is similar to CMOS circuits except few changes which make this logic

more energy efficient than CMOS with lesser delay as compared to 2PASCL as well as

circuits also [8]. The notable difference between LPHS and static

CMOS logic gate is the two diodes, one from the output node to the power clock supply and

another one is placed next to the nMOS logic to another power clock. Both PN diodes are used to

cycle the charges from the output node, to improve discharging speed of internal signal nodes.

This is especially advantageous for signal nodes with a long chain of switches.

-level sinusoidal power clock supplies, Vø and Vø bar are used to

Substrate of pMOS is connected to Vø whereas for nMOS, it is

connected to Vø bar. From the simulation, we found that split- level sinusoidal gives a lower

energy dissipation compared to trapezoidal power clock supply even if we set the Trise

the trapezoidal waveforms to maximum values. By using two split-level sinusoidal waveforms

peak is 0.9 V, we can reduce the voltage difference, thus reducing the

charging and discharging activities. Sinusoidal waveforms can also be generated with higher

energy efficiency than trapezoidal waveforms.

–

hen the output node is LOW and pMOS tree is turned ON, Load

capacitor is charged through pMOS transistor resulting in the HIGH state at the

is LOW and nMOS is ON, no transition occurs. The same result is

when the output node is HIGH and pMOS is ON. Finally, when output

HIGH and nMOS is ON, discharging via nMOS takes place resulting in the decrease of

(threshold voltage) value where the logical state is “0” [9

International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012

127

Proposed circuit, Low Power High Speed (LPHS)

de uses in 2PASCL logic circuit.

100MHz, capacitances acting on MOS diode in 2PASCL charges and

capacitances of

For low power

digital design [7] it has always been the focus point of the engineers to keep the load capacitance

LPHS Adiabatic logic is similar to CMOS circuits except few changes which make this logic

2PASCL as well as

PHS and static

CMOS logic gate is the two diodes, one from the output node to the power clock supply and

another one is placed next to the nMOS logic to another power clock. Both PN diodes are used to

ischarging speed of internal signal nodes.

level sinusoidal power clock supplies, Vø and Vø bar are used to

Substrate of pMOS is connected to Vø whereas for nMOS, it is

level sinusoidal gives a lower

rise and Tfall of

level sinusoidal waveforms

peak is 0.9 V, we can reduce the voltage difference, thus reducing the

ated with higher

hen the output node is LOW and pMOS tree is turned ON, Load

capacitor is charged through pMOS transistor resulting in the HIGH state at the output.

is LOW and nMOS is ON, no transition occurs. The same result is

output node is

resulting in the decrease of

9].](https://image.slidesharecdn.com/3512vlsics10-190316120800/85/DESIGN-ANALYSIS-OF-A-CHARGE-RE-CYCLE-BASED-NOVEL-LPHS-ADIABATIC-LOGIC-CIRCUITS-FOR-LOW-POWER-APPLICATIONS-5-320.jpg)

![International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012

II. Hold phase: Now due to the diodes, the state of

remains unchanged. When the preliminary state of the output node is HIGH, it will

change to Vt, the threshold voltage of the diode. At this point, discharging via diode D1

occurs.

From the operation of LPHS adiabatic logic as explained in

dynamic switching are observed as circuit nodes are not necessarily

every clock cycle which reduces the node switching activities significantly. Th

lowers the switching activity lowering the

4. CIRCUIT SIMULATION

Schematic design and simulation

shown where comparison has been made for

conventional CMOS and 2PASCL logic circuits with their power dissipation, delay and PDP.

These results well conform for ul

The simulation in this paper were performed using a SPECTRE circuit simulator with a 0.18 um,

1.8 V standard CMOS process. The width and Length of the nMOS and pMOS logic gates were

0.6 um and 0.18 um respectively. A load capacitance of 0.01 pF was connected to the output

node. The frequency of the power supply clock was set to a value same as the transition

frequency. In this era of digital integrated circuits [

degradation in the logic levels is the objective and the authors with the result have tried to prove

this point.

4.1. Simulation Results

The logic function of these fundamental logic

are based on LPHS Adiabatic logic

accordingly as shown in the corresponding

tabulated. The time scale on the horizontal axis is in terms of nsecs. Th

usual meaning.

i. Schematic and Simulated waveforms of

Vø

Figure 6(a). Schematic and simulated waveform of LPHS Adiabatic

International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012

ue to the diodes, the state of output when preliminary state is LOW

remains unchanged. When the preliminary state of the output node is HIGH, it will

to Vt, the threshold voltage of the diode. At this point, discharging via diode D1

From the operation of LPHS adiabatic logic as explained in evaluation and hold

dynamic switching are observed as circuit nodes are not necessarily charging and discharging

every clock cycle which reduces the node switching activities significantly. This

lowering the energy dissipation.

IMULATION AND RESULTS

and simulation results of INVERTER, NAND, NOR, XOR and 2:1 MUX

where comparison has been made for a non cascaded gate to those design using

conventional CMOS and 2PASCL logic circuits with their power dissipation, delay and PDP.

These results well conform for ultra low power applications using these logic gates [9].

were performed using a SPECTRE circuit simulator with a 0.18 um,

1.8 V standard CMOS process. The width and Length of the nMOS and pMOS logic gates were

m respectively. A load capacitance of 0.01 pF was connected to the output

node. The frequency of the power supply clock was set to a value same as the transition

In this era of digital integrated circuits [10] maintaining the logic level with le

degradation in the logic levels is the objective and the authors with the result have tried to prove

of these fundamental logic circuits which may form a basic cell for a design

based on LPHS Adiabatic logic and has been observed that the circuits conform

corresponding figures. The results have been categorized

The time scale on the horizontal axis is in terms of nsecs. The other symbols have their

Schematic and Simulated waveforms of different logic circuits

Vout

CL

Schematic and simulated waveform of LPHS Adiabatic Inverter.

International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012

128

when preliminary state is LOW

remains unchanged. When the preliminary state of the output node is HIGH, it will

to Vt, the threshold voltage of the diode. At this point, discharging via diode D1

hold phase, less

charging and discharging on

is significantly

of INVERTER, NAND, NOR, XOR and 2:1 MUX are

a non cascaded gate to those design using

conventional CMOS and 2PASCL logic circuits with their power dissipation, delay and PDP.

tra low power applications using these logic gates [9].

were performed using a SPECTRE circuit simulator with a 0.18 um,

1.8 V standard CMOS process. The width and Length of the nMOS and pMOS logic gates were

m respectively. A load capacitance of 0.01 pF was connected to the output

node. The frequency of the power supply clock was set to a value same as the transition

] maintaining the logic level with less

degradation in the logic levels is the objective and the authors with the result have tried to prove

circuits which may form a basic cell for a design

conform to operate

results have been categorized and well

e other symbols have their

Inverter.](https://image.slidesharecdn.com/3512vlsics10-190316120800/85/DESIGN-ANALYSIS-OF-A-CHARGE-RE-CYCLE-BASED-NOVEL-LPHS-ADIABATIC-LOGIC-CIRCUITS-FOR-LOW-POWER-APPLICATIONS-6-320.jpg)

![International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012

134

Load Capacitance (fF)

Figure 12. Delay (ns) Versus CL comparison

Load Capacitance (fF)

Figure 13. PDP Versus CL comparison

The functionality of the proposed circuit with variation in different parameters (like load

capacitance, frequency and voltage) has been examined. Using proposed adiabatic logic [11], we

can reduce delay upto 40% compared with the 2PASCL. LPHS reduces delay at the cost of power

dissipation and output swing of the circuit. Output swing reduces from 0.5-1.8 to 0.7-1.8.

Further, it is important to note that the clock plays a very important role for these type of digital

circuits not because charge recycling has been employed but due the dependence power

consumption on it, there whether single phase clock is being used on two phase it is utmost

important to control the clock [11-14].

5. CONCLUSION

This paper primarily focuses on the design of low power high speed CMOS cell structures. A

family of full-custom conventional CMOS Logic and an Adiabatic Logic units were designed in

Cadence Design Architect using standard TSMC 0.18 µm technology and further the analysis of

0

0.2

0.4

0.6

0.8

1

1.2

0 50 100 150

CMOS

QAL

Pseudo nmos QAL

Pseudo nmos with

diode adiabatic

0

1

2

3

4

5

6

7

0 50 100 150

QAL

Pseudo nmos QAL

Pseudo nmos with

diode

CMOS](https://image.slidesharecdn.com/3512vlsics10-190316120800/85/DESIGN-ANALYSIS-OF-A-CHARGE-RE-CYCLE-BASED-NOVEL-LPHS-ADIABATIC-LOGIC-CIRCUITS-FOR-LOW-POWER-APPLICATIONS-12-320.jpg)

![International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.5, October 2012

135

the average dynamic power dissipation and delay with respect to the load capacitance was done.

It was found that the Proposed adiabatic logic style is advantageous in applications where power

reduction as well as speed is of prime importance as in high performance battery-portable digital

systems running on batteries such as note-book computers, cellular phones, personal digital

assistants, etc. We have achieved an improvement of 60 to 70% in power consumption as

compared with Conventional CMOS circuits. This reduction in power consumption is achieved

by adiabatic logic with split level power supply. The comparison of the 2PASCL circuit with

Conventional CMOS has proved that power consumption with 2PASCL logic is far less as

compared to CMOS based technique but delay increases. Delay comparatively increases in

2PASCL but using modified logic we can optimize the circuit between delay, power and output

swing.

ACKNOWLEDGEMENTS

The authors duly acknowledged with gratitude the support from ministry of communication and

information technology, DIT Govt. of India, New Delhi, through special manpower Development

program in VLSI and related Software’s Phase-II (SMDP-II) project in ECE Department, MNNIT

Allahabad-211004, India.

REFERENCES

[1] N. Anuar, Y. Takahashi and T. Sekine, “Two phase clocked adiabatic static CMOS logic and its

Logic Family,” Joural of Semiconductor Technology & Science. Vol.10 No.1, Mar. 2010.

[2] N. Anuar, Y. Takahashi and T. Sekine, “Two phase clocked adiabatic static logic circuit: a proposal

for digital low power applications,” Proc. IEICE Gen. Conf., p.102, Mar. 2009.

[3] T. Indermauer and M. Horowitz, “Evaluation of Charge Recovery Circuits and Adiabatic Switching

for Low Power Design,” Technical Digest IEEE Symposium Low Power Electronics, San Diego, pp.

102-103, October 2002.

[4] W. C. Athas, J. G. Koller, L. Svensson, “An Energy- Efficient CMOS Line Driver using Adiabatic

Switching,” Fourth Great Lakes symposium on VLSI, California, March 2005.

[5] Y. Ye, and K. Roy, “QSERL: Quasi-static energy recovery logic,” Solid-States Circuits., IEEE

Journal, Vol.36, Issue 2, Feb., 2001, pp. 239-248.

[6] N. Waste and K. Eshraghian, Principle of CMOS VLSI Design: A System Prospective, 2nd ed. New

York: Addison – Wesley, 1993.

[7] A. P. Chandrakashan, S. Sheng, and R. W. Brodersen, “Low Power CMOS Digital Design,” IEEE

Journal of Solid-state Circuits, Vol. 27, No. 04, pp. 473-484, April 1999.

[8] W.C.Athes, L.J. Svensson, J.G. Koller, et al., “Low-power digital systems based on adiabatic-

switching principles,” IEEE Trans. On VLSI Systems, 2(4): 398-407, December 1994.

[9] A.Blotti and R. Saletti, “Ultralow- Power Adiabatic Circuit Semi-Custom Design,” IEEE

Transactions on VLSI Systems, vol. 12, no. 11, pp. 1248-1253, November 2004.

[10] Sung Mo Kang and Yusuf Leblebici, CMOS Digital Integrated Circuits - Analysis and Design,

McGraw-Hill, 2003.

[11] S. Samantha “Adiabatic computing: A Contemporary Review,” International conference on

computers and devices for communication, Dec. 2009, pp.1-4

[12] J. Marjonen and M Aberg, “A single clocked adiabatic static logic – a proposal for digital low power

application,” J. VLSI signal processing, vol.27, no. 27, Feb.2001, pp.253-268.

[13] B.Voss and M. Glesner, “A Low Power Sinusoidal Clock,” In Proc. of the International Symposium

on Circuits and Systems, ISCAS 2001.

[14] Y. Moon and D. K. Jeong, “An Efficient Charge Recovery Logic Circuit,” IEEE JSSC, Vol. 31, No.

04, pp. 514-522, April 1996.](https://image.slidesharecdn.com/3512vlsics10-190316120800/85/DESIGN-ANALYSIS-OF-A-CHARGE-RE-CYCLE-BASED-NOVEL-LPHS-ADIABATIC-LOGIC-CIRCUITS-FOR-LOW-POWER-APPLICATIONS-13-320.jpg)