Functional verification using System verilog introduction

- 2. Content • Functional Verification • Verification Process • Introduction to SV HVL • Data Types

- 3. Functional Verification: • Test Bench produces the stimulus and stimulus given to the DUV (Design Under Verification) then DUV produces the output, and output collected by test bench • We always choose the direct test cases to verify the functionality • Most important question would be, how we going to find bugs, more bugs and faster • That’s where we look a new methodologies like “constrained Random Driven Verification • As direct test cases time consuming, we look into new languages called system Verilog

- 5. Verification Process: Test-n Test-2 Test-1 DUT Specifications + Verification Plan Coverage closure Verification signoff DUT for Synthesis PM DUT Spec V Plan Test case writers Test Bench Developers DUT TB Environ ment TB Implementation Regression Testing

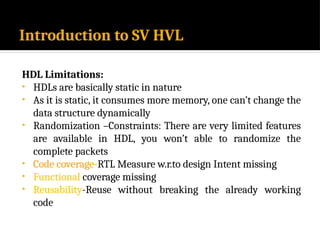

- 6. Introduction to SV HVL HDL Limitations: • HDLs are basically static in nature • As it is static, it consumes more memory, one can’t change the data structure dynamically • Randomization –Constraints: There are very limited features are available in HDL, you won’t able to randomize the complete packets • Code coverage-RTL Measure w.r.to design Intent missing • Functional coverage missing • Reusability-Reuse without breaking the already working code

- 7. Introduction to SV HVL System Verilog HDVL: • A set of extensions to Verilog -2001 • An unified language for design and verification • A language which supports all the verification • Constrained Random Coverage Driven Verification • Assertion based verification • Functional Coverage • A language which supports object oriented programming

- 8. Introduction to SV HVL System Verilog Sources: • System Verilog is an IEEE standard language based on Verilog 2001 • System Verilog extensions come from a number of sources including : • C & C++ : Data types and Object Oriented Programming • PSL: Assertion based Verification • VERA: Randomization • VHDL: enum, Packages • DPI(Direct Programming Interface): from Synopsys • System Verilog makes interface easily

- 9. Data Types: Verilog 2001 • Two main groups of data types-nets and registers • Four values 0,1,X and Z • Register data types-reg, integers, time and real • Stores values-static storage • Are assigned in a procedural block(initial /always) Example: reg [15:0] data_bus; //16-bit unsigned variable int counter; //32-bit signed variable real float_num; //64-bit unsigned floating point numbers time sim_time; //64-bit unsigned Variable

- 10. Data Types: System Verilog • logic: 4-state data type (similar to reg) • Two state data types • enum: Declares a variable • typedef: user defined Data Type • struct and class

- 11. Data Types: logic • logic- functionality is similar to reg • Logic data type can be used anywhere that the reg and net data types are used, except with inout ports • The logic datatype is synthesizable, and it an used to define both combinational and sequential logic • Confusion in Verilog HDL, reg datatype can be used for both combinational and sequential but in hardware reg [Register] refers to sequential

- 12. Data Types: logic Example: module tb_dff( ); parameters CYCLE=20; logic q,q_b,d,clk,rst_n; initial begin clk=0; rst_n; forever #(CYCLE/2) clk=~clk; @(negedge clk) rst_n=1; @(negedge clk) d=1; end assign q_b=~q diff DUT(q, d, clk, rst_n);//DUT instantiation endmodule:tb_dff

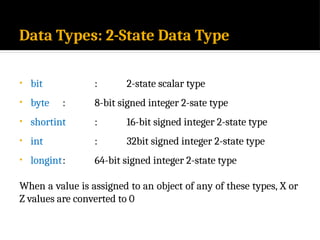

- 13. Data Types: 2-State Data Type • bit : 2-state scalar type • byte : 8-bit signed integer 2-sate type • shortint : 16-bit signed integer 2-state type • int : 32bit signed integer 2-state type • longint: 64-bit signed integer 2-state type When a value is assigned to an object of any of these types, X or Z values are converted to 0

- 14. Data Types: 2-State Data Type Example: bit clk; //2-state , bit value : 0 or 1 bit [31:0]vbus; //2 state 32-bits unsigned integer int cnt; //2 state 32-bits signed integer int unsigned cnt; // 2 state 32-bits unsigned integer byte crc_byte; //2-state 8-bits signed integer shortint sint; //2-state 16-bits signed integer longint lint; //2-state 64-bits signed integer

- 15. Data Types: Struct Type Struct Types: • Struct –collection of data static • Array of different data types • Synthesizable • Subset of class-use class for TB Example: struct{bit[7:0] address; logic [7:0] payload[0:63]; enum [Good, Error, ] pkt_type; logic [7:0] parity}packet; packet.adress=8’d25; packet.pkt_type=Error;

- 16. Data Types: User Defined Type Typedef used to define a user defined data type typedef bit[31:0]word_t; word_t word1,word2; struct{ bit[7:0] r,g,b;}pixel; pixel.r=8’d25; pixel.g=8’d255; pixel.b=8’d11; typedef struct{bit [7:0] r,g,b;}pixel_st; pixel_st samsung_pixel; pixel_st sony_pixel; samsung_pixel.r=8’d25; sony_pixel=‘{8’d38,8’d98,8’d69};

- 17. Data Types: Enumerated • Enum-enumerated data type(list of values) enum{init, read, write, brd, bwr}fsm_state; fsm_state=init; fsm_state=read; Example: typedef enum {init,read,write,brd,bwr}fsm_state_et; fsm_state_et Pre_state,Next_state; fsm_state_et state=state.first; initial begin $display(“%s:%d”,state.name, state); if(state==state.last(1)) break; state=state.next(); end

- 18. Data Types: Enumerated • Default values can be given to constants Ex: typedef enum{init, read=2, write, brd=7, bwr} fsm_state; • Built in methods: 1. first() : //returns first element 2. last() : //returns last element 3. next() : //returns next element 4. prev() : //returns previous element 5. next(N) : //returns Nth next element 6. prev(N) : //returns Nth previous element

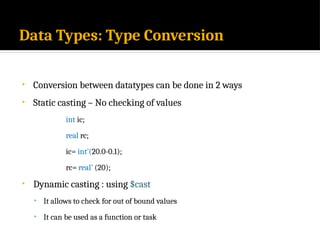

- 19. Data Types: Type Conversion • Conversion between datatypes can be done in 2 ways • Static casting – No checking of values int ic; real rc; ic= int’(20.0-0.1); rc= real’ (20); • Dynamic casting : using $cast • It allows to check for out of bound values • It can be used as a function or task

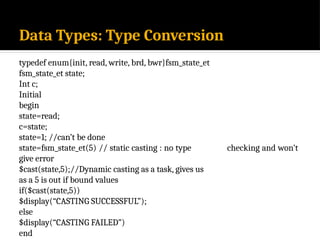

- 20. Data Types: Type Conversion typedef enum{init, read, write, brd, bwr}fsm_state_et fsm_state_et state; Int c; Initial begin state=read; c=state; state=1; //can’t be done state=fsm_state_et(5) // static casting : no type checking and won’t give error $cast(state,5);//Dynamic casting as a task, gives us as a 5 is out if bound values if($cast(state,5)) $display(“CASTING SUCCESSFUL”); else $display(“CASTING FAILED”) end

- 21. Data Types: Strings • Variable length – grows automatially • Memory is dynamically allocated string str; initial begin str=“Rgukt_Sklm”; str=str.tolower();//rgukt_sklm $display(“Character in 5th position is ”,str.getc(5)): str.putc(5, “-”); // “_” is replaced with “-” $display(“%s”, str.substr(6,str.len-1)); //sklm is printed str={str, “.com”};//rgukt-sklm.com str={{3{w}}, “.”,str}; disp($sformat(“https://%s”,str); end task disp(string s); $display(“at time t=%d, %s”, $time,s); //at time t=0, https://www.rgukt-sklm.com endtask

- 22. Data Types: Packages • User defined packages • Define type definitions, functions and global variables for reuse throughout the design or verification environment • Good for functions like printing error messages, reading/writing a bos etc. • Good for reusable environment –test cases import the packages

- 23. Data Types: Packages Example: package pkg; int no_of_trans; function void display(string s); $display($time,”%s,n=%d”,s,no_of_trans); endfunction endpackage module A import pkg::*; initial begin #1; no_of_trans=10; #1; display(“From Module A:”); end endmodule

- 24. Data Types: Packages module B import pkg::*; initial begin #4; no_of_trans=20; display(“From Module B:”); end endmodule Result: 2, From Module A, n=10 4, From Module B, n=20

- 25. SV Memories :Packed Arrays • Some times you may want to access the entire array value and also divide it into smaller elements • For example, A 32-bit register can be considered as a group of four 8-bit registers or a group of 32 bits • SV Packed array is treated as both an array and a single value //$-bytes packed into 32-bits bit [3:0][7:0]byte_packed; byte_packed=32’h5454_5454; $displayh(byte_packed,byte_packed[0],byte_packed[0][0]); Show all 32 bits Least significant byte Least significant bit

- 26. SV Memories :Multidimensional Arrays //unpacked Arrays of 3 packed elements bit[3:0][7:0] bytes[0:2] bytes [0]=32’d255; bytes [0][3]=8’d255; bytes [0][1][6]=1’b1;

- 27. SV Memories :Accessing the elements of an Arrays logic [31:0] msrc[5], mdst[5]; initial begin for (int i=0; i< $size (msrc);i++); mdst[j]=msrc[j]*4; end int mda [3][3]=‘{‘{0,1,2},’{3,4,5},’{6,7,8}}; initial begin foreach(mda[I,j]) $display(“mda[%0d][%0d]=%0d”,I,j,mda[i][j]) end

- 28. SV Memories : Array –Aggregate copy and compare bit [31:0] msrc[5]={0,1,2,3,4}, mdst[5]={5,4,3,2,1}; //copy and compare all values without any loop initial begin if(msrc==mdst) //compare all msrc values with mdst $display(“msrc is equal to mdst”); else $display(“msrc is not equal to mdst”); mdst=msrc //copy all values to mdst //Compare 4 values of msrc with mdst if(msrc[1:4]==mdst[1:4]) $display(“msrc is equal to mdst”); else $display(“msrc is not equal to mdst”); end

- 29. SV Memories : Dynamic Arrays • Packed arrays –size to be defined before compilation • How can we define the array size to store random number if packets • Random number of packets could be less than the maximum value expected leads to memory wastage • SV provides dynamic memory which can be allocated and resized dynamically during simulation

- 30. SV Memories : Dynamic Arrays • Variable size single dimension memory-size changes dynamically during run time int da1[],da2[]; initial begin da1=new[10];//Allocate 10 elements foreach (da1[i]) //initializing da1[i]=i; da2=da1; //copying da1=new[30]da(da1); //Allocate 30 new & copy existing int da1=new[100]; //Allocate 100-new ints-old values are lost da2.delete( ); //Delete all elements of da2 end

- 31. SV Memories : Queues • Size of the Queue grows and shrinks automatically-No need to define the size; before running simulation • Dynamic array size should be allocated with a fixed value-needs size before the usage • Queue-New elements can be added/removed easily • Queue-Elements can be accessed from any location deirectly using index • Flexible Memory-Variable sizing • Single dimension array with automatic sizing • Many searching, sorting and insertion methods Syntax: type name[$]

- 32. SV Memories : Queues int qm1[$]={1,3,4,5,6}; int qm2[$]={2,3}; int k=2; qm1.insert(1,k); //K-insert before ‘3’ qm1.delete(1); //Delete the element #1 qm1.push_front(7); //insert at front k=qm1.pop_back(); //k=6 qm2.push_back(4); // insert at back K=qm2.pop_front(); //k=2 foreach(qm1[i]) $display(qm1[i]); // display the element of the entire queue qm2.delete(); //delete entire queue

- 33. SV Memories : Associative Arrays • How do you model the memories of huge size-10GB RAM • You may write data into only very few locations of 10GM RAM • Allocating 10GB might lead to either wastage of memory or running out of memory • Associative arrays: memory will be allocated only writing the data • Associative arrays : Memory read and write can happen in non- contiguously Example: • Great for creating memory models –sparse memories • Dynamically allocated, non-contiguous elements • Accessed with integer, or string index • Great for spare arrays with wide ranging index • Builtin functions: exists, first, last, next, prev Syntax: type name[*];

- 34. SV Memories : Associative Arrays Example: • Great for creating memory models –sparse memories • Dynamically allocated, non-contiguous elements • Accessed with integer, or string index • Great for spare arrays with wide ranging index • Builtin functions: exists, first, last, next, prev Syntax: type name[*]; All Memory Allocated, even unused elements Un used Elements don’t use memory Standard Array Associative Array

- 35. SV Memories : Array Methods • Array methods can be used only with unpacked arrays • Fixed, Dynamic, Queue, and associative Arrays int cnt, sa; int da[ ]={10,1,8,3,5,5}; cnt=da.sum with(item>7); //2:[10,8] Sa=da.sum with(item==5); //2:[5,5] //Sorting Methods int da[ ]={10,1,7,3,4,4}; da.revrse( ); //{4,4,3,7,1,10} da.sort( ); //{1,3,4,4,7,10} da.rsort( ); //{10,7,4,4,3,1} da.shuffle( ); //{10,4,3,7,1,4}

- 36. SV Memories : Array Methods //Array locator methods: min, max unique int da[6]=[1,5,2,6,8,6]; int mq[$]; mq=da.min( );//[1] mq=da.max( );//[8] mq=da.unique( );//[1,5,2,8,6] int da[6]={1,6,2,6,8,6}; mq=f.find_first with (item>5); //[6] mq=f.find_first_index with (item>5); //[1] da[1]=6 mq=f.find_last with (item>5); //[6] mq=f.find_last_index with (item>5); //[5] da[5]=6

![Data Types: Verilog 2001

• Two main groups of data types-nets and registers

• Four values 0,1,X and Z

• Register data types-reg, integers, time and real

• Stores values-static storage

• Are assigned in a procedural block(initial /always)

Example:

reg [15:0] data_bus; //16-bit unsigned variable

int counter; //32-bit signed variable

real float_num; //64-bit unsigned floating point numbers

time sim_time; //64-bit unsigned Variable](https://image.slidesharecdn.com/systemverilogunit-1-241217174545-4c9579fb/85/Functional-verification-using-System-verilog-introduction-9-320.jpg)

![Data Types: logic

• logic- functionality is similar to reg

• Logic data type can be used anywhere that the reg and net

data types are used, except with inout ports

• The logic datatype is synthesizable, and it an used to define

both combinational and sequential logic

• Confusion in Verilog HDL, reg datatype can be used for both

combinational and sequential but in hardware reg [Register]

refers to sequential](https://image.slidesharecdn.com/systemverilogunit-1-241217174545-4c9579fb/85/Functional-verification-using-System-verilog-introduction-11-320.jpg)

![Data Types: 2-State Data Type

Example:

bit clk; //2-state , bit value : 0 or 1

bit [31:0]vbus; //2 state 32-bits unsigned integer

int cnt; //2 state 32-bits signed integer

int unsigned cnt; // 2 state 32-bits unsigned integer

byte crc_byte; //2-state 8-bits signed integer

shortint sint; //2-state 16-bits signed integer

longint lint; //2-state 64-bits signed integer](https://image.slidesharecdn.com/systemverilogunit-1-241217174545-4c9579fb/85/Functional-verification-using-System-verilog-introduction-14-320.jpg)

![Data Types: Struct Type

Struct Types:

• Struct –collection of data static

• Array of different data types

• Synthesizable

• Subset of class-use class for TB

Example:

struct{bit[7:0] address;

logic [7:0] payload[0:63];

enum [Good, Error, ] pkt_type;

logic [7:0] parity}packet;

packet.adress=8’d25;

packet.pkt_type=Error;](https://image.slidesharecdn.com/systemverilogunit-1-241217174545-4c9579fb/85/Functional-verification-using-System-verilog-introduction-15-320.jpg)

![Data Types: User Defined Type

Typedef used to define a user defined data type

typedef bit[31:0]word_t;

word_t word1,word2;

struct{ bit[7:0] r,g,b;}pixel;

pixel.r=8’d25;

pixel.g=8’d255;

pixel.b=8’d11;

typedef struct{bit [7:0] r,g,b;}pixel_st;

pixel_st samsung_pixel;

pixel_st sony_pixel;

samsung_pixel.r=8’d25;

sony_pixel=‘{8’d38,8’d98,8’d69};](https://image.slidesharecdn.com/systemverilogunit-1-241217174545-4c9579fb/85/Functional-verification-using-System-verilog-introduction-16-320.jpg)

![SV Memories :Packed Arrays

• Some times you may want to access the entire array value and also

divide it into smaller elements

• For example, A 32-bit register can be considered as a group of four

8-bit registers or a group of 32 bits

• SV Packed array is treated as both an array and a single value

//$-bytes packed into 32-bits

bit [3:0][7:0]byte_packed;

byte_packed=32’h5454_5454;

$displayh(byte_packed,byte_packed[0],byte_packed[0][0]);

Show all 32 bits

Least significant byte Least significant bit](https://image.slidesharecdn.com/systemverilogunit-1-241217174545-4c9579fb/85/Functional-verification-using-System-verilog-introduction-25-320.jpg)

![SV Memories :Multidimensional Arrays

//unpacked Arrays of 3 packed elements

bit[3:0][7:0] bytes[0:2]

bytes [0]=32’d255;

bytes [0][3]=8’d255;

bytes [0][1][6]=1’b1;](https://image.slidesharecdn.com/systemverilogunit-1-241217174545-4c9579fb/85/Functional-verification-using-System-verilog-introduction-26-320.jpg)

![SV Memories :Accessing the elements of an Arrays

logic [31:0] msrc[5], mdst[5];

initial

begin

for (int i=0; i< $size (msrc);i++);

mdst[j]=msrc[j]*4;

end

int mda [3][3]=‘{‘{0,1,2},’{3,4,5},’{6,7,8}};

initial

begin

foreach(mda[I,j])

$display(“mda[%0d][%0d]=%0d”,I,j,mda[i][j])

end](https://image.slidesharecdn.com/systemverilogunit-1-241217174545-4c9579fb/85/Functional-verification-using-System-verilog-introduction-27-320.jpg)

![SV Memories : Array –Aggregate copy and compare

bit [31:0] msrc[5]={0,1,2,3,4},

mdst[5]={5,4,3,2,1};

//copy and compare all values without any loop

initial

begin

if(msrc==mdst) //compare all msrc values with mdst

$display(“msrc is equal to mdst”);

else

$display(“msrc is not equal to mdst”);

mdst=msrc //copy all values to mdst

//Compare 4 values of msrc with mdst

if(msrc[1:4]==mdst[1:4])

$display(“msrc is equal to mdst”);

else

$display(“msrc is not equal to mdst”);

end](https://image.slidesharecdn.com/systemverilogunit-1-241217174545-4c9579fb/85/Functional-verification-using-System-verilog-introduction-28-320.jpg)

![SV Memories : Dynamic Arrays

• Variable size single dimension memory-size changes dynamically

during run time

int da1[],da2[];

initial

begin

da1=new[10];//Allocate 10 elements

foreach (da1[i]) //initializing

da1[i]=i;

da2=da1; //copying

da1=new[30]da(da1); //Allocate 30 new & copy existing int

da1=new[100]; //Allocate 100-new ints-old values are lost

da2.delete( ); //Delete all elements of da2

end](https://image.slidesharecdn.com/systemverilogunit-1-241217174545-4c9579fb/85/Functional-verification-using-System-verilog-introduction-30-320.jpg)

![SV Memories : Queues

• Size of the Queue grows and shrinks automatically-No need to

define the size; before running simulation

• Dynamic array size should be allocated with a fixed value-needs

size before the usage

• Queue-New elements can be added/removed easily

• Queue-Elements can be accessed from any location deirectly using

index

• Flexible Memory-Variable sizing

• Single dimension array with automatic sizing

• Many searching, sorting and insertion methods

Syntax: type name[$]](https://image.slidesharecdn.com/systemverilogunit-1-241217174545-4c9579fb/85/Functional-verification-using-System-verilog-introduction-31-320.jpg)

![SV Memories : Queues

int qm1[$]={1,3,4,5,6};

int qm2[$]={2,3};

int k=2;

qm1.insert(1,k); //K-insert before ‘3’

qm1.delete(1); //Delete the element #1

qm1.push_front(7); //insert at front

k=qm1.pop_back(); //k=6

qm2.push_back(4); // insert at back

K=qm2.pop_front(); //k=2

foreach(qm1[i])

$display(qm1[i]); // display the element of the entire queue

qm2.delete(); //delete entire queue](https://image.slidesharecdn.com/systemverilogunit-1-241217174545-4c9579fb/85/Functional-verification-using-System-verilog-introduction-32-320.jpg)

![SV Memories : Associative Arrays

• How do you model the memories of huge size-10GB RAM

• You may write data into only very few locations of 10GM RAM

• Allocating 10GB might lead to either wastage of memory or running

out of memory

• Associative arrays: memory will be allocated only writing the data

• Associative arrays : Memory read and write can happen in non-

contiguously

Example:

• Great for creating memory models –sparse memories

• Dynamically allocated, non-contiguous elements

• Accessed with integer, or string index

• Great for spare arrays with wide ranging index

• Builtin functions: exists, first, last, next, prev

Syntax: type name[*];](https://image.slidesharecdn.com/systemverilogunit-1-241217174545-4c9579fb/85/Functional-verification-using-System-verilog-introduction-33-320.jpg)

![SV Memories : Associative Arrays

Example:

• Great for creating memory models –sparse memories

• Dynamically allocated, non-contiguous elements

• Accessed with integer, or string index

• Great for spare arrays with wide ranging index

• Builtin functions: exists, first, last, next, prev

Syntax: type name[*];

All Memory

Allocated, even

unused

elements

Un used

Elements don’t

use memory

Standard Array Associative Array](https://image.slidesharecdn.com/systemverilogunit-1-241217174545-4c9579fb/85/Functional-verification-using-System-verilog-introduction-34-320.jpg)

![SV Memories : Array Methods

• Array methods can be used only with unpacked arrays

• Fixed, Dynamic, Queue, and associative Arrays

int cnt, sa;

int da[ ]={10,1,8,3,5,5};

cnt=da.sum with(item>7); //2:[10,8]

Sa=da.sum with(item==5); //2:[5,5]

//Sorting Methods

int da[ ]={10,1,7,3,4,4};

da.revrse( ); //{4,4,3,7,1,10}

da.sort( ); //{1,3,4,4,7,10}

da.rsort( ); //{10,7,4,4,3,1}

da.shuffle( ); //{10,4,3,7,1,4}](https://image.slidesharecdn.com/systemverilogunit-1-241217174545-4c9579fb/85/Functional-verification-using-System-verilog-introduction-35-320.jpg)

![SV Memories : Array Methods

//Array locator methods: min, max unique

int da[6]=[1,5,2,6,8,6];

int mq[$];

mq=da.min( );//[1]

mq=da.max( );//[8]

mq=da.unique( );//[1,5,2,8,6]

int da[6]={1,6,2,6,8,6};

mq=f.find_first with (item>5); //[6]

mq=f.find_first_index with (item>5); //[1] da[1]=6

mq=f.find_last with (item>5); //[6]

mq=f.find_last_index with (item>5); //[5] da[5]=6](https://image.slidesharecdn.com/systemverilogunit-1-241217174545-4c9579fb/85/Functional-verification-using-System-verilog-introduction-36-320.jpg)