Implementation of page table

- 1. Implementation & Structure of Page Table

- 2. AgendaPage Table DefinitionImplementation of Page TableHardware SupportPaging Hardware With TLBMemory ProtectionPage Table StructureHierarchical PagingShared PagesInverted Page TablesHashed Page Tables

- 3. Page Table DefinitionA page table is the data structureused by a virtual memory systemin a computer operating system to store the mapping between virtual addresses and physical addresses

- 4. Two concern to discussImplementation of Page Tableconcerning about the access time of page table and load it to main memoryPage Table Structure concerning about the page table size & structure implementation

- 5. Implementation of Page Table(Hardware Support)The hardware implementation of the page table can be done in several ways. In the simplest case, the page table is implemented as a set of dedicated registers. These registers should be built with very high-speed logic to make the paging-address translation efficient.Problem with page size…..

- 6. Hardware SupportPage table is kept in main memory.Page-table base register (PTBR) points to the page table.Page-table length register (PRLR) indicates size of the page table.In this scheme every data/instruction access requires two memory accesses. One for the page table and one for the data/instructionProblem with access time…..

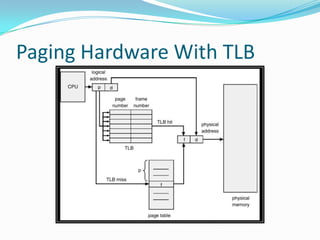

- 7. Paging Hardware With TLBThe CPU's memory management unit (MMU) stores a cache of recently used mappings from the operating system's page table. This is called the translation look a side buffer (TLB).

- 8. Paging Hardware With TLBThe TLB may reside between the CPU and the CPU cache, between the CPU cache and primary storage memory, or between levels of a multi-level cache.The TLB is typically implemented as content-addressable memory (CAM).The TLB is associative, high-speed memory. Each entry in the TLB consists of two parts: a key (or tag) and a value.

- 9. Paging Hardware With TLBAssociative memory – parallel search Address translation (A´, A´´)If A´ is in associative register, get frame # out. Otherwise get frame # from page table in memoryPage #Frame #

- 10. Paging Hardware With TLBTLB HitTLB MissIf the TLB is already full of entries, the operating system must select one for replacementaddress-space identifiers (ASIDs)Page fault

- 11. Paging Hardware With TLB

- 12. Paging Hardware With TLBEffective Access TimeAssociative Lookup = time unitAssume memory cycle time is 1 microsecondHit ratio – percentage of times that a page number is found in the associative registers; ration related to number of associative registers.Hit ratio = Effective Access Time (EAT) EAT = (1 + ) + (2 + )(1 – ) = 2 + –

- 13. Paging Hardware With TLBSuppose: TLB lookup takes 5 nano sec. Memory access time is 100 nano sec. Hit ratio (probability to find page number in TLB) is ? Effective Access Time = (5+100)* ? +( 5+100+100)*(1- ?) Suppose ? = 80% (for example, TLB size = 16) EAT = 105*.8 + 205*.2 = 125 nano sec. Suppose ? = 98% (for example, TLB size = 64) EAT = 105*.98 + 205*.02 = 107 nano sec

- 14. Memory ProtectionMemory protection implemented by associating protection bit with each frame.-One bit can define a page to be read-\Write or read-onlyValid-invalid bit attached to each entry in the page table:“valid” indicates that the associated page is in the process’ logical address space, and is thus a legal page.“invalid” indicates that the page is not in the process’ logical address space.page-table length register (PTLR), to indicate the size of the page table.

- 16. Page Table StructureMost modern computer systems support a large logical address space(2^32 to 2^64). In such an environment, the page table itself becomes excessively large. For example, consider a system with a 32-bit logical address space. If the page size in such a system is 4 KB (212 ), then a page table may consist of up to 1 million entries (2^32/2^12). Assuming that each entry consists of 4 bytes, each process may need up to 4 MB of physical address space for the page table alone.

- 17. Hierarchical Page TablesKnowing as Multilevel PagingThe page table might be too big to fit in a contiguous space, so we may have a hierarchy with several levelsBreak up the logical address space into multiple page tables.A simple technique is a two-level page table, three-level page table.

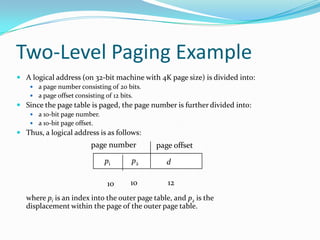

- 19. Two-Level Paging ExampleA logical address (on 32-bit machine with 4K page size) is divided into:a page number consisting of 20 bits.a page offset consisting of 12 bits.Since the page table is paged, the page number is further divided into:a 10-bit page number. a 10-bit page offset.Thus, a logical address is as follows:where pi is an index into the outer page table, and p2 is the displacement within the page of the outer page table.page numberpage offsetp2pid101210

- 20. Three-Level Paging ExampleA logical address (on 64-bit machine with 4K page size) is divided into:The next step Would be a four-level paging scheme,

- 21. Address-Translation SchemeAddress-translation scheme for a two-level 32-bit paging architecture

- 22. Performance of Hierarchical PagingSuppose: Three level paging TLB lookup takes 5 nano sec. Memory access time is 100 nano sec. Hit ratio (probability to find page number in TLB) is ? Effective Access Time = (5+100)* ? +( 5+300+100)*(1- ?) Suppose ? = 80% (for example, TLB size = 16) -EAT = 105*.8 + 405*.2 = 165 nano sec. Suppose ? = 98% (for example, TLB size = 64) -EAT = 105*.98 + 405*.02 = 111 nano sec.

- 23. Shared PagesShared codeOne copy of read-only (reentrant) code shared among processes (i.e., text editors, compilers, window systems). Shared code must appear in same location in the logical address space of all processes.Private code and data Each process keeps a separate copy of the code and data.The pages for the private code and data can appear anywhere in the logical address space.

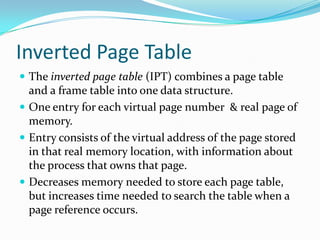

- 25. Inverted Page TableThe inverted page table (IPT) combines a page table and a frame table into one data structure.One entry for each virtual page number & real page of memory.Entry consists of the virtual address of the page stored in that real memory location, with information about the process that owns that page.Decreases memory needed to store each page table, but increases time needed to search the table when a page reference occurs.

- 26. Inverted Page TableUse hash table to limit the search to one — or at most a few — page-table entries.Say goodbye to sharing ? -because there is only one virtual page entry for every physical page, one physical page cannot have two (or more) shared virtual addresses.

- 27. Inverted Page Table Architecture

- 28. Hashed Page TablesCommon in address spaces > 32 bits.The virtual page number is hashed into a page table. This page table contains a chain of elements hashing to the same location.Each element consists of three fields: (1) the virtual page number,(2) the value of the 111apped page frame, (3) a pointer to the next element in the linked list.Virtual page numbers are compared in this chain searching for a match. If a match is found, the corresponding physical frame is extracted.

- 30. THANK YOU

Editor's Notes

- #7: If we want to access location i, we must first index into the page table, using the value in the PTBR offset by the page number for ch8/8.This task requires a memory access. It provides us with the frame number which is combined with the page offset to produce the actual address. We can then access the desired place in memory

- #8: MMU is a computer hardware component responsible for handling accesses to memory requested by the CPU. Its functions include translation of virtual addresses to physical addresses, memory protection, cache control

- #9: Content-addressable memory (CAM) is a special type of computer memory used in certain very high speed searching applicationsUnlike standard computer memory (random access memory or RAM) in which the user supplies a memory address and the RAM returns the data word stored at that address, a CAM is designed such that the user supplies a data word and the CAM searches its entire memory to see if that data word is stored anywhere in it

- #10: When the associative memory is presented with an item, the item is compared with all keys simultaneously. If the item is found,the corresponding value field is returned

- #11: -When a logical address is generated by the CPU, its page number is presented to the TLB. If the page number is found , its frame number is immediately available and is used to access memory. The whole task may take less than 10 percent longer than it would if an unmappedmemory reference were used. If the page number is not in the TLB (known as a TLB miss)-In addition, we add the page number and frame number to the TLB, so that they will be found quickly on the next reference.-Some TLBs store address-space identifiers (ASIDs) in each TLB entry. An ASID uniquely identifies each process and is used to provide address-space protection for that process. When the TLB attempts to resolve virtual page numbers, it ensures that the ASID for the currently running process matches the ASID associated with the virtual page. If the ASIDs do not match, the attempt is treated as a TLB miss.-If the TLB is already full of entries, the operating system must select one for replacement. Replacement policies range from least recently used (LRU) to random.-page fault is an interrupt (or exception) to the software raised by the hardware, when a program accesses a page that is mapped in address space, but not loaded in physical memory

- #12: .

- #15: in the form of a page-table length register (PTLR), to indicate the size of the page table. This value is checked against every logical address to verify that the address is in the valid range for the process. Failure of this test causes an error trap to the operating system

- #26: The inverted page table (IPT) combines a page table and a frame table into one data structure at its core is a fixed-size table with the number of rows associating to each frame in memory. If there were 4000 frames, the inverted page table has 4000 rows. For each row there is an entry for the virtual page number (VPN), the physical page number (not the physical address), some other data and a means for creating a collision chain,

- #27: A simple technique for addressing this issue is to allow the page table to contain only one mapping of a virtual address to the shared physical address. This meansthat references to virtual addresses that are not mapped result in page faults.