Implementation of quantum gates using verilog

- 1. Implementation of Quantum Gates Presentation by SHASHANK KUMAR Defence Institute of Advance Technology, Pune Supervisor Dr. Anbuselvi M. Associate Professor Department of Electronics Engineering

- 2. Contents • Objective • Introduction • Module/ Block diagram/ Project overview • Proposed Solution • Conclusion • References

- 3. Objective • To get explored with the concepts of Quantum computing • To gain knowledge on basic quantum circuits using Qiskit • To model various quantum gates with the basic of the quantum circuits also making universal gate-NAND in the Quantum circuit which will also shows the reversible nature.

- 4. Introduction • Quantum circuits are collections of quantum gates interconnected by quantum wires. The actual structure of a quantum circuit, the number and the types of gates, as well as the interconnection scheme are dictated by the unitary transformation. • A physical implementation of a qubit could use the two energy levels of an atom. An excited state representing |1> and a ground state representing |0>. • A single qubit can be forced into a superposition of the two states denoted by the addition of the state vectors: |> = |0> + |1> • Where and are complex numbers and | | + | | = 1

- 5. BLOCH SPHERE

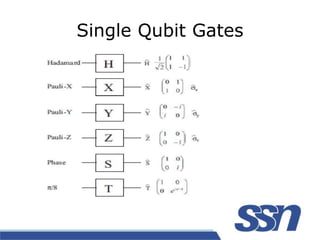

- 6. Quantum Gates • One Qubit Gates are- H gate, Pauli-X,Y,Z gates, Identity gates, square root of NOT gate • Two Qubit Gates are- CNOT gate, Controlled Z gate, Controlled Phase gate, Swap gate • Three Qubit Gates are- Toffeli gate, Controlled sq. Z gate, Controlled sq. Phase gate, Controlled Swap

- 10. Fig: Multi Qubit gates

- 11. Project Module/Block diagram Fig: Quantum circuit for NAND There are three main components in this quantum circuit- 1. Initialization and Reset 2. Quantum Gates 3. Measurements

- 12. Proposed Solution With the help of quantum gates I will be designing the classical gates.

- 13. Programming • Design of reversible gates and various applications of it using Verilog HDL with Xilinx ISE version 13.1, spartan 3 FPGA. • Xilinx ISE is a software tool produced by Xilinx for synthesis and analysis of HDL designs. This tool enables the developer to synthesize their designs, perform time analysis, examine RTL diagrams, design reactions to different stimuli, and configure the target device with the programmer.

- 14. Fig: Simulation of NAND gate performed on Xilinx ISE Design Suit

- 15. Conclusion Though in our description of quantum circuits we use the concepts input and output registers of qubits, we should be aware that physically, the input and the output of a quantum circuit are not separated as their classical counterparts are, this convention allows us to describe the effect of unitary transformation carried out by the circuit in a more coherent fashion.

- 16. References • https://en.wikipedia.org/wiki/Quantum_computing • https://www.bernardmarr.com/default.asp?contentID=1143 • https://www.livescience.com/65651-quantum-computers-get-scary-fast.html • https://www.ibm.com/quantum-computing/learn/what-is-quantum-computing/ • https://www.youtube.com/watch?v=C6MLmESU9v0 • https://www.youtube.com/watch?v=V1Cx8wCZN_c • https://en.wikipedia.org/wiki/Quantum_superposition • https://becominghuman.ai/quantum-superposition-and-what-that-means-to- quantum-computation-3fbb5a711b9a