Synopsys User Group Presentation

- 1. Andrew Gardner ASIC prototyping with Certify 12 th May2009

- 2. 1. Who are we? 2. Why do we prototype an ASIC? 3. A History of FPGAs in Lund and Basingstoke 4. The Process used in Lund and Basingstoke 5. Differences between ASIC and FPGA 6. ASIC partitioning example

- 3. Department overview The ASIC prototyping team in Ericsson is split between sites the UK and Sweden. We have been providing ASIC-like prototype and demonstrator platforms into the organisation for over 10 years We have a proven delivery track record Our platform customers used the A1 FPGA prototype to make the first WCDMA (3G) calls months before ASIC samples were available. The department consists of 5 engineers in Lund and 3 in Basingstoke. It is responsible for the platform hardware & firmware development as well as customer support.

- 4. Why do we prototype an ASIC? To aid software development Software have been our main official customer for; driver dev., OS porting and architecture validation. Heavy usage by many different departments System covers for ASIC delays and is used to validate ASIC ECO fixes up until ASIC tape-out and beyond To support Boot and DSP ROM code development An essential part of the verification environment especially for Boot ROM with its dependencies on system architecture and external interfaces We get ASIC verification Seen as "for free", not a planned/controlled part of the ASIC strategy – ‘Hard to find’ bugs have been discovered on all major projects. Interoperability with IP and system using "real" application software Verifying new concept/system/architecture. To aid hardware development ITP (Industrial Test Program) Interoperability between prototype and different hardware including mixed signal, radio and bridge ASICs

- 5. FPGA A1 Platform: 2001 – 2003 (Xilinx Virtex-E & Altera Apex) Used to prototype our first generation of Digital BaseBand ASICs Used to make “real time” WCDMA and GSM calls over the air Major success – “From now on, all new DBB ASIC designs should be emulated” ..EMP management (2003) Dual-mode radio Wide-band (FPGA WANDA) Peripherals card FPGA (one of seven) Graphics add-on Radio port Colour display FPGA prog. card UART ports

- 6. FPGA A2 Platform: 2004 – 2007 (Altera Stratix I & II) Used to prototype second generation Digital BaseBand ASICs Modular platform utilising ASIC reference design hardware I/F

- 7. FPGA B500 Platform: 2007 – today (Xilinx Virtex-5) Used to prototype the latest Ericsson Baseband ASIC designs Generic platform with access and application personality boards

- 8. Current hardware platform (early 2007) Largest, fastest FPGA parts Key benefits Flexible Stable User friendly Good performance Robust Future proof Easy to support Generic architecture

- 9. Hardware features State of the art FPGA parts for maximum capacity, performance and interconnect Single main board and close component proximity to maximise performance and robustness Best utilisation of I/O to maximise system partition options Switched buses with fine granularity offers flexible interconnect tuning options Firmware control of hardware configuration removes user error and allows complete reconfiguration as and when required Additional plug-in ‘personality’ board makes generic FPGA board suitable for a wide variety of uses Support FPGA containing MicroBlaze system integrated with compact flash offers a great deal of flexibility On board cooling, status display, metal frame, compact flash programming and encapsulated power unit make unit robust and user friendly Simple ‘personality’ hardware plug-in designed to accept existing reference design hardware Xilinx Virtex-5 LX330 In excess of 1000 inter-FPGA I/O available 480 I/O switchable in increments of 8 System hardware covered by high coverage boundary-scan test All clocking and switch controls managed by support FPGA Large amount of flexible I/O routed to I/F connectors, some direct, some decoupled through support FPGA Soft control functions coupled with MicroBlaze allow complete flexibility in firmware A more integrated and tidier solution compared to previous generations of hardware Existing hardware is used as much as possible

- 10. Key benefits Low staffing requirements Maximum use of verified ASIC RTL database with the aim of minimum (FPGA specific) modifications Fast turn-around time for new and incremental builds due to efficient tool methodology High degree of re-use from ASIC; scripting, ASIC level verification tests Semi-automated scripted tool flow once project is ‘up and running’ All prototype projects have been delivered functional platforms to customers well in advance of ASIC samples

- 11. The FPGA Design Flow PROTOTYPE VOB RTL CERTIFY EDIF NETLIST & CONSTRAINT FILES XILINX PLACE & ROUTE FPGA PROG. BIT-STREAMS 4 4 BOARD DESC. FILE 4 1 DELIVERY TIMING REPORTS Design Files Partition Zippering Timing Info. Pin Assigns … FPGA SPECIFIC VOB ASIC VOB 1 ASIC LEVEL VERIFICATION VOB Regression SW Encryption Keys SRS SRS SRS SRS PROTOTYPE HARDWARE TIMING FILES

- 12. Certify front-end Option to export to a higher performance synthesis tools such as Premier. Flexible implementation strategy as easy to experiment with and to optimize design partitions. No need to re-simulate or to use formal verification. Fast turn-around when an incremental release is required (new RTL rev.) Techniques to allow logic replication, splitting of Muxes/high fan-in logic elements, register balancing. Complete management of manually assisted I/O signal allocations. Time budget calculation for each FPGA within the system partition. Powerful design browser allowing interactive schematic expansion. Opportunities to use bottom-up and modular design approaches. Tool efficiently handles conversion of ASIC like gated clock structures. Manual interactive partitioning of very large mixed code designs in an extremely short time compared to an RTL restructuring approach.

- 13. ARM AHB Bus Matrix Partitioning

- 14. ARM AHB Bus Matrix Partitioning

- 15. ARM AHB Bus Matrix Partitioning

- 16. Example wide-band modem design partition FPGA WCDMA Subsystem A H B - L i t e 52 MHz ( 104 MHz ) 52 MHz MC RAM point to point links I / O Control bus CPU / DSP MMU I / F Memory AHB IF 26 MHz P o i n t t o p o i n t 2 6 M H z Internal Clock Frequency ( 5 ) + / / / - + + 3 . 84 MHz 7 . 68 Mhz 15 . 36 MHz 52 MHz Slot counter 16 chip strobe 16 chip counter ( 104 MHz ) 26 MHz AHB IF 26 MHz AHB IF 26 MHz All WCDMA interrupts 2 6 M H z XXXXXX XXXXXX 26 MHz XXXXXX Rx - stage 1 XXXXXXXXX XXXXXXXXX XXXXXX 52 MHz 15 . 36 MHz XX RAM XXXXXX 15 . 36 MHz 3 . 84 MHz XXXXXX 15 . 36 MHz Path Searcher 1 PS RAM 104 MHz 15 . 36 MHz XXXXXX XX RAM 15 . 36 MHz 7 . 68 MHz 3 . 84 MHz XXXXXX XX RAM 15 . 36 MHz XXXXXX 15 . 36 MHz XXXXXX 1 - XXXXXX XXXXXX 15 . 36 MHz 3 . 84 MHz XXXXXX XXXXXX XXXXXXXXX XXX RAM XXX RAM XXX RAM M M U 52 MHz Slot counter 16 chip strobe 16 chip counter & 8 bits I & Q XXXXXX XXXXXX 15 . 36 MHz 8 bits I & Q , 0 1 16 bits x 2 RSSI XXXXXX 26 MHz XXXXXX XXXXXX XX RAM 16 16 To DIGRF 32 , 2 32 , 2 AHB Bus Matrix 52 MHz Memory with retention Proprietary bus WSS Sub - block s XXXXXX 26 MHz 7 . 68 MHz XXXXXX 26 MHz 7 . 68 MHz XXXXXX 7 . 68 MHz XXXXXX 26 MHz 1 & & IOs TX 32 (+ 3 to DIIGRF ) XXXXXX 26 MHz 15 . 36 MHz 52 MHz 15 . 36 MHz To DIGRF XX RAM 15 . 36 MHz ( 208 MHz ) 52 MHz Dual interface 7 . 68 MHz FIFO ahb 26 to ahb 52 26 MHz 26 MHz 52 MHz 26 MHz 52 MHz 52 MHz 52 MHz 26 MHz 26 MHz FPGA specific FPGA D 3000 Ahb 26 to ahb 52 26 to 52 bridge Wb _ memory _ controller _ bridge _ rec _ play 26 to 52 bridge _ _ _ Wb _ memory _ controller _ bridge _ tx _ stage _ 3 26 to 52 bridge FPGA D2000 D 3000 D 2000 26 MHz 52 MHz 52 MHz 52 MHz ( 104 MHz ) ( 104 MHz ) mm _ ahb _ 26 to 52 _ bridge ( 104 MHz ) ( 104 MHz ) ( 104 MHz ) ( 104 MHz ) ( 104 MHz ) ( 104 MHz ) ( 104 MHz ) ( 1 0 4 M H z ) ( 104 MHz ) 52 MHz ( 104 MHz ) _ _ ( 104 MHz ) ( 104 MHz ) ( 104 MHz ) ( 104 MHz ) ( 104 MHz ) ( 104 MHz ) ( 104 MHz ) Psearch 0 _ ahb _ 26 to 52 _ bridge ( 104 MHz ) ( 104 MHz ) ( 208 MHz ) ( 104 MHz ) ( 208 MHz ) ( 52 MHz ) 26 MHz 52 MHz ( 104 MHz ) ( 104 MHz ) ( 1 0 4 M H z ) ( 104 MHz ) ahb 26 to ahb 52 ahb 26 to ahb 52 Strobe width comp . tx 3 _ strb _ width _ comp 3 R E M O V E D H assium _ prototype _ WCDMA _ _ _ / - Doc respons / Approved Product name Rev Date Prepared Reference Document no Sheet - 1 - FPGA D3000

- 17. Timescales and resources (FPGA firmware only) Kylie ASIC: 1 engineer - 6 months (also providing customer support) First Firmware release to core Software teams after 7 weeks based on stable RTL. ~20 weeks before first ASIC samples are available . Core Software team achieve OS boot within 4 weeks of initial firmware delivery. ~16 weeks before first ASIC samples are available . ASIC samples arrive and within 4 hours are up and running using both the FPGA test environment and real software.

- 18. 5. Differences between ASIC and FPGA

- 19. Differences between ASIC and FPGA We endeavour to replicate the functionality of the ASIC but usually have to compromise in the following areas… Speed Depending on the application, speed may or may not be an issue. Analyse customer requirements, use fast parts, request that designs meet required performance in FPGA Memories Memories are usually ASIC specific and must be ported to FPGA types. All FPGA specific memories must be validated High performance external interfaces Such interfaces (e.g. DDR EMIF) contain complex front-end logic to maintain timing alignment. When running at reduced rates on FPGA this logic can be simplified to ease implementation Processor choice ‘ Soft’ implementations can be virtually identical to ASIC albeit operating at reduced frequency. External test chip type processors may differ in; clocking, reset, functionality, memory sizes and may be prone to bugs as they are often poorly verified by the vendor Test logic Test logic structures are always tied off in an inactive state and subsequently optimized away by the tool flow Clocking Clock control structures may be simplified to ease porting to FPGA. It is not uncommon for a flexible multi-frequency strobe type ASIC structure to be replaced with a fixed frequency PLL based arrangement for FPGA. Also clock multiplex structures are usually removed due to their fundamental incompatibility with FPGA architectures

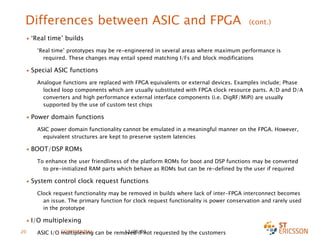

- 20. Differences between ASIC and FPGA (cont.) ‘ Real time’ builds ‘ Real time’ prototypes may be re-engineered in several areas where maximum performance is required. These changes may entail speed matching I/Fs and block modifications Special ASIC functions Analogue functions are replaced with FPGA equivalents or external devices. Examples include; Phase locked loop components which are usually substituted with FPGA clock resource parts. A/D and D/A converters and high performance external interface components (i.e. DigRF/MiPi) are usually supported by the use of custom test chips Power domain functions ASIC power domain functionality cannot be emulated in a meaningful manner on the FPGA . However, equivalent structures are kept to preserve system latencies BOOT/DSP ROMs To enhance the user friendliness of the platform ROMs for boot and DSP functions may be converted to pre-initialized RAM parts which behave as ROMs but can be re-defined by the user if required System control clock request functions Clock request functionality may be removed in builds where lack of inter-FPGA interconnect becomes an issue. The primary function for clock request functionality is power conservation and rarely used in the prototype I/O multiplexing ASIC I/O multiplexing can be removed if not requested by the customers

- 21. THANK YOU - Questions?