Task allocation on many core-multi processor distributed system

- 1. WEBINAR: TASK ALLOCATION ON MANY CORE-MULTI-PROCESSOR Deepak Shankar Founder Mirabilis Design Inc. Email: [email protected]

- 2. Agenda Task allocation- Concept and challenges Definition of Task Graph Assignment of task graph to single, multi and custom resources Example of large-scale design- 5G and Radar Case Study About Mirabilis Design Inc. 8/19/2020 MIRABILIS DESIGN INC. 2

- 3. Introduction to Task Allocation And Resource Planning

- 4. Task Allocation Task allocation is ◦ The assignment of tasks in a behavior or data flow ◦ To a set of resources Allocation depends on ◦ Dynamic behavior of processors, SoC and embedded systems Decisions are made based on ◦ Timing deadline, buffer consumption and data loss 8/19/2020 MIRABILIS DESIGN INC. 4

- 5. Resource Allocation Resource allocation is easy but smart, efficient resource allocation is challenging Impacts of under- and over-allocation can be felt in ◦ Timing deadlines ◦ Cost ◦ Peripheral elements such as power consumption, size and thermal planning Resource allocation strategy must be considered prior to any development Resources include ◦ Software queues and semaphores ◦ Hardware processors and memory ◦ Network VPN and message passing interfaces 8/19/2020 MIRABILIS DESIGN INC. 5

- 6. Task Allocations and Timing Deadline T3 Expected T3 Complete Consider three tasks- T1, T2 and T3 All tasks allocated to a single resource Each Task has processing time (Equal) and priority (T1>T2>T3) Design Impacts of buffering, preemption, offset times and processing capacity Challenges must be studied globally, ideally in the context of power, performance, and reliability

- 7. Simulating Task Allocations 8/19/2020 MIRABILIS DESIGN INC. 7 Tasks arriving with slight offset Assignment has First Come-First Serve Tasks arriving with slight offset Assignment is First Come-First Serve with Preemption

- 8. Application Task Graph (Implementation can be in HW or SW)

- 9. Impact of Single Constraint to Task Graph 8/19/2020 MIRABILIS DESIGN INC. 9 Low processing time with entry queue Low processing time with entry queue A1 has slightly elevated processing time

- 10. Map 4 Tasks to 4 Cores using Scheduler 8/19/2020 MIRABILIS DESIGN INC. 10 • Concurrent threads with variable processing times • Assign offset time between tasks • No preemption • Trade-off between 1,2,3 or 4 processing resources • Introduction of a scheduler or dispatcher • Incorporate additional constraint of power consumed by resources

- 11. Power, Resource Usage and Latency 8/19/2020 MIRABILIS DESIGN INC. 11 All threads arrive at the same time Each thread has a 3.5ms offset from the next one Each thread has a 3.5ms offset from the next one Single Core

- 12. Modeling Multi Processor Full System Complex behavior - input stream - data dependent behavior Contention - limited resources - scheduling/arbitration Interference of multiple applications - limited resources - scheduling/arbitration - anomalies I/O DSP CPU1 CPU2 task1 task2 task3 task4 Scheduling software tasks using limited resources

- 13. Map Tasks to Multi-Processor Hardware Library Folder Parameters Reports & Statistics Platform Architecture Application 1 Application 2 Workload Single view for abstract to detailed modeling Power Table

- 14. Varying Hardware Attributes 8/19/2020 MIRABILIS DESIGN INC. 14 Bus Speed=400Mhz Bus Speed=200Mhz

- 15. Application of Task Graph, Task Allocation In Industrial Design

- 16. Introduction to Dynamic System Modeling Architecture Exploration ◦ Optimize and validate the system specification ◦ Specification: Processor speed, topology and arbitration ◦ Requirements: Timing, energy, cost, weight and efficiency Performance Analysis ◦ Buffer size, utilization, throughput and response time Power Measurement ◦ Peak and average power, energy and power/task Functional Correctness ◦ Arbitration, software task scheduling and task graph Failure Analysis ◦ Hardware, Software, network, data, power and logic Making Better Quality Products

- 17. Test Resource Model with Task State Machine Thermal UAV model (VisualSim) Start Cruise Loiter ISR Stop Ascend Descend UAV testcase (VisualSim) Mechanical structure (fixed for given model) Power system HW SW RF DL GPS Data flow Power, thermal connection Hardware Software RF Power Thermal Implementation level design uses existing processes HW and SW blocks form Avionics RF Datalink include transmitter and receiver Key performance of Avionics and RF Datalink are constrained by input power and temperature GPS performance (sensitivity) is constrained by RF interference caused by RF Datalink and temp Testcase determines power available with respect to time to functional blocks under simulation Augment current functional systems engineering with timing and power

- 18. • By changing the amount of video input data (packet number), observe the Interface -> DRAM transfer performance and examine the upper limit performance of the video input that the system can tolerate. Evaluating data throughput for Memory-Intensive Application 18 210Packet/Sec 12ms 21Packet/Sec 414us 300Packet/Sec • 250 Packet/Sec is the system limit • With 300 Packet/Sec, simulation cannot be executed due to FIFO buffer overflow.

- 19. Task Allocation for a Radar Data flow

- 20. Mapping 5G Baseband to Hardware Platform 8/19/2020 MIRABILIS DESIGN INC. 20

- 21. Case Study: Comparing RISC-V and ARM-A53 processors For a Braking Application

- 22. Block Structure and Scenario 8/19/2020 MIRABILIS DESIGN INC. 22 Wheel1 Wheel2 Wheel3 Wheel4 Brake Pedal Proximity Sensor Gyro Sensor Gateway ECU Database 1 Database 2 Database 3 Database 4 Road condition sensor Power Analysis Engine CAN BUS CAN BUS CAN BUS N N N N NN NN NN N N N N CAN Wire CAN Node

- 23. 8/19/2020 MIRABILIS DESIGN INC. 23 VisualSim Model ARM-A53, RISC-V Parameters Database CAN Bus CAN Nodes Power Which Libraries? Configuration blocks and data table setting SENSORS • Traffic • Expression List NETWORK • CAN Bus/CAN Node ECU • Processor • Bus Arbiter • DMA • RAM • PCIe • AMBAAXI FETCH DATA • Database • Variable List • Routing table POWER • Power Manager Logics to create script block - CAN Bus/CAN Node - Switch Gateway

- 24. 8/19/2020 MIRABILIS DESIGN INC. 24 Various Results Display of Speed VS Time Latency of Wheels with respect to Time Power evaluation Evaluation of state of the road VS Time Detailed Statistics of Gateway Statistics Debug Messages

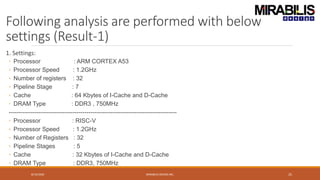

- 25. Following analysis are performed with below settings (Result-1) 1. Settings: ◦ Processor : ARM CORTEX A53 ◦ Processor Speed : 1.2GHz ◦ Number of registers : 32 ◦ Pipeline Stage : 7 ◦ Cache : 64 Kbytes of I-Cache and D-Cache ◦ DRAM Type : DDR3 , 750MHz ------------------------------------------------------------------------------------ ◦ Processor : RISC-V ◦ Processor Speed : 1.2GHz ◦ Number of Registers : 32 ◦ Pipeline Stages : 5 ◦ Cache : 32 Kbytes of I-Cache and D-Cache ◦ DRAM Type : DDR3, 750MHz 8/19/2020 MIRABILIS DESIGN INC. 25

- 26. 8/19/2020 MIRABILIS DESIGN INC. 26 Analysis Result - 1 ① Latency - Time between Brake Pedal (Manual Operation) or Proximity Sensor (Autonomous Driving) and Wheel brake ARM CORTEX-A53 has better latency performance than RISC-V processor Latency Analysis - ARM CORTEX A53 Processor Latency Analysis - RISC-V Processor

- 27. 8/19/2020 MIRABILIS DESIGN INC. 27 Analysis Result - 1 ① Power - Power consumption of ARM CORTEX A53 and RISC-V Processor Power Table block Defines power consumption specifications Watt value to Standby/Active/Wait/Ideal • Clock • Voltage Power analysis - ARM CORTEX A53 Processor Power analysis - RISC-V Processor RISC-V have worse power performance than ARM CORTEX-A53 processor

- 28. 8/19/2020 MIRABILIS DESIGN INC. 28 Analysis Result - 1 ① MIPS - MIPS(Million Instruction per second) vs Task Latency MIPS analysis - ARM CORTEX A53 Processor Task Latency analysis - ARM CORTEX A53 Processor Here you can see, Whenever the Task Latency is high or reaching peak the performance of MIPS dips Task Latency (Peak)

- 29. 8/19/2020 MIRABILIS DESIGN INC. 29 MIPS analysis - RISC-V Processor Task Latency analysis - RISC-V Processor ① MIPS - MIPS(Million Instruction per second) vs Task Latency Analysis Result – 1 (Cont..) Task Latency (Peak) Here you can see, Whenever the Task Latency is high or reaching peak the performance of MIPS dips

- 31. Introduction to VisualSim Architect ◦ Architect processors, hardware systems, software and network ◦ Map algorithms on integrated and distributed systems ◦ Compute resource requirements for application task graphs ◦ Test compliance to standards and generation of diagnostics Timing and Throughput Power measurement, management and Battery Entire EE to Semiconductor Functional and Safety Analysis Libraries Hardware, Software and Network Graphical Modeling Functional, timing and power analysis to existing Model-based System Design

- 32. Largest Systems-Level Model Library Largest library of traffic, resources, hardware, software and analysis Traffic • Distribution • Sequence • Trace file • Instruction profile Reports • Timing and Buffer • Throughput/Util • Ave/peak power • Statistics Power • State power table • Power management • Energy harvesters • Battery • RegEx operators SoC Buses • AMBA and Corelink • AHB, AB, AXI, ACE, CHI, CMN600 • Network-on-Chip • TileLink System Bus • PCI/PCI-X/PCIe • Rapid IO • AFDX • OpenVPX • VME • SPI 3.0 • 1553B Processors • GPU, DSP, mP and mC • RISC-V • Nvidia- Drive-PX • PowerPC • X86- Intel and AMD • DSP- TI and ADI • MIPS, Tensilica, SH ARM • M-, R-, 7TDMI • A8, A53, A55, A72, A76, A77 Custom Creator • Script language • 600 RegEx fn • Task graph • Tracer • C/C++/Java • Python Support • Listener and Trace • Debuggers • Assertions Stochastic • FIFO/LIFO Queue • Time Queue • Quantity Queue • System Resource • Schedulers • Cyber Security RTOS • Template • ARINC 653 • AUTOSAR Memory • Memory Controller • DDR DRAM 2,3,4, 5 • LPDDR 2, 3, 4 • HBM, HMC • SDR, QDR, RDRAM Storage • Flash & NVMe • Storage Array • Disk and SATA • Fibre Channel • FireWire Networking • Ethernet & GiE • Audio-Video Bridging • 802.11 and Bluetooth • 5G • Spacewire • CAN-FD • TTEthernet • FlexRay • TSN & IEEE802.1Q FPGA • Xilinx- Zynq, Virtex, Kintex • Intel-Stratix, Arria • Microsemi- Smartfusion • Programmable logic template • Interface traffic generator Software • GEM5 • Software code integration • Instruction trace • Statistical software model • Task graph Interfaces • Virtual Channel • DMA • Crossbar • Serial Switch • Bridge RTL-like • Clock, Wire-Delay • Registers, Latches • Flip-flop • ALU and FSM • Mux, DeMux • Lookup table

- 33. About Mirabilis Design Founded in 2003 and based in Sunnyvale, CA, USA. Development and support centers in US, India, China, Korea and Czech Republic Focused on system architecture exploration of electronics, semiconductors and software 40+ customers worldwide in Semiconductors, Aerospace, Computing and Automotive VisualSim- Modeling and simulation software Largest source of system modeling IP with embedded timing and power 100’s of man years experience in system design and exploration of digital electronics Select the “Right” configuration to match customer request

- 34. WEBINAR: TASK ALLOCATION ON MANY CORE-MULTI-PROCESSOR Deepak Shankar Founder Mirabilis Design Inc. Email: [email protected] Thank You