Verification flow and_planning_vlsi_design

- 1. Introduction to Verification of VLSI Design and Functional Verification 1 Dr Usha Mehta 04-08-2021 Usha Mehta, Ph.D. in Testing and Verification of VLSI Design [email protected] [email protected]

- 2. Acknowledgement….. This presentation has been summarized from various books, papers, websites and presentations on VLSI Design and its various topics all over the world. I couldn’t item-wise mention from where these large pull of hints and work come. However, I’d like to thank all professors and scientists who created such a good work on this emerging field. Without those efforts in this very emerging technology, these notes and slides can’t be finished. 2 Dr Usha Mehta 04-08-2021

- 9. Source of Errors • Errors in Specification • Unspecified Functionality • Conflicting requirements • Unrealized features • No model for checking as it is at top of abstraction hierarchy • Errors in Implementation • human error in interpreting design functionality 9 Dr Usha Mehta 04-08-2021

- 10. How to reduce human introduced errors in interpretation? • Automation • Poka-Yoke 10 Dr Usha Mehta 04-08-2021

- 11. • Automation • The obvious way to reduce human introduced error • It is not always possible specially when the processes are not well defined and requires a human ingenuity and creativity. • Poka-Yoke • A Japanese term that means "mistake- proofing" or “inadvertent error prevention” • Towards the fool automation but not complete automation • Human intervention is needed only to decide on the particular sequence or steps required to obtain the desired results. • Verification now a days remains an art. 11 Dr Usha Mehta 04-08-2021

- 12. Redundancy • Most costly but highly efficient approach • Most widely used for ASICs 12 Dr Usha Mehta 04-08-2021

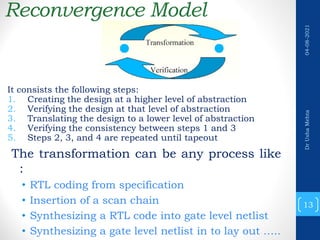

- 13. Reconvergence Model It consists the following steps: 1. Creating the design at a higher level of abstraction 2. Verifying the design at that level of abstraction 3. Translating the design to a lower level of abstraction 4. Verifying the consistency between steps 1 and 3 5. Steps 2, 3, and 4 are repeated until tapeout The transformation can be any process like : • RTL coding from specification • Insertion of a scan chain • Synthesizing a RTL code into gate level netlist • Synthesizing a gate level netlist in to lay out ….. 13 Dr Usha Mehta 04-08-2021

- 15. Verification Methods • Functional Verification • Formal Verification • Equivalence Checking • Model Checking • Semiformal Verification • Assertion Based Methods 15 Dr Usha Mehta 04-08-2021

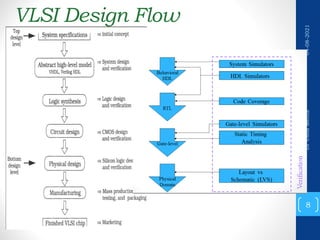

- 16. Verification Techniques • Simulation (functional and timing) • Behavioral • RTL • Gate-level (pre-layout and post-layout) • Switch-level • Transistor-level • Formal Verification (functional) • Binary Decision Diagrams • Equivalence Checking • Model Checking • Static Timing Analysis (timing) 16 Dr Usha Mehta 04-08-2021

- 18. Thanks……