Verilog overview

- 1. Verilog Overview MAHMOUD HAGHIGHI WWW.POSEDGE.IR VERILOG OVERVIEW12/20/2015 1

- 2. Overview Verilog Basics Simulation Tools VERILOG OVERVIEW12/20/2015 2

- 3. Overview A Hardware Description Language (HDL) is a language used to describe a digital system, for example, a computer or a component of a computer. A digital system can be described at several levels: Switch level: wires, resistors and transistors Gate level: logical gates and flip flops Register Transfer Level (RTL): registers and the transfers of information between registers. Two Major HDLs in Industry • VHDL • Verilog VERILOG OVERVIEW12/20/2015 3

- 4. Verilog vs. VHDL VHDL “V” is short for Very High Speed Integrated Circuits. Designed for and sponsored by US Department of Defense. Designed by committee (1981-1985). Syntax based on Ada programming language. Was made an IEEE Standard in 1987. Verilog Was introduced in 1985 by Gateway Design System Corporation, now a part of Cadence Design Systems, Inc.'s Systems Division. Was made an IEEE Standard in 1995 Syntax based on C programming language. Design examples using Verilog HDL ◦ Intel Pentium, AMD K5, K6, Atheon, ARM7, etc ◦ Thousands of ASIC designs using Verilog HDL VERILOG OVERVIEW12/20/2015 4

- 6. Verilog HDL Models HDL model specifies the relationship between input signals and output signals. In Verilog, A “module” contains the hardware description of the circuit. Verilog code for a AND gate Module definition Ports definition Module Structure VERILOG OVERVIEW12/20/2015 6

- 7. Numbers Numbers are specified using the following form <size><base format><number> Examples: ◦ x = 347 // decimal number ◦ x = 4’b101 // 4- bit binary number 0101 ◦ x = 16’h87f7 // 16-bit hex number h87f7 ◦ x = 2’b101010 ◦ x = 2’d83 size of the number in bits. ’b (binary) ’d (decimal) ’o(octal) ’h(hex). VERILOG OVERVIEW12/20/2015 7

- 8. operators Bitwise Operators ~ NOT & AND | OR ^ XOR ~| NOR ~& NAND ^~ or ~^ XNOR Logical & Relational Operators !, &&, | |, ==, !=, >=, <=, >, < VERILOG OVERVIEW12/20/2015 8

- 9. Ports There are three different port types: • Input • Output • Inout Port definition: • <port type> <portwidth> <port name> • Example: A(7:0) B(7:0) C my_module U1 A(7:0) B(7:0) C VERILOG OVERVIEW12/20/2015 9

- 10. Data Types: Variables Two basic families of data types for variables: Nets and Registers Net variables – e.g. wire • Memory less • Variable used simply to connect components together • Usually corresponds to a wire in the circuit. Register variables – e.g. reg • Variable used to store data as part of a behavioral description • Like variables in ordinary procedural languages Note: • reg should only be used with always and initial blocks (to be presented …) • The reg variables store the last value that was procedurally assigned to them whereas the wire variables represent physical connections between structural entities such as gates. A(7:0) W(7:0) C L K A D Fub1 U1 DA CLK VERILOG OVERVIEW12/20/2015 10

- 11. Continuous Assignment Continuous statement is used to model combinational logic. A continuous assignment statement is declared as follows: assign <net_name> = variable; assign corresponds to a connection. Target is never a reg variable. Examples: VERILOG OVERVIEW12/20/2015 11

- 12. Continuous Assignment Verilog code for a 4 bit adder: VERILOG OVERVIEW12/20/2015 12

- 13. Procedural Assignment Used for modeling sequential circuits. A procedural assignment statement is declared as follows: Always @(event list) begin <reg_name> <= variable; end The assignment will be performed whenever one of the events in “event_list” occurs. VERILOG OVERVIEW12/20/2015 13

- 14. Procedural Assignment Example: D-FF VERILOG OVERVIEW12/20/2015 14 D clk Out

- 15. Interconnecting Modules In order to use a module, it should be instantiated: <Module_name> <Instant_name> (<port mapping>) Example: using two mux2 to build a mux4 (actually this is not an mux4-1 !!!) In(1 :0 ) O ut se l mux2_i1 mux2In4(3:0) sel4(1:0) In(1 :0 ) O ut se l mux2_i2 mux2 In4(3:2) In4(1:0) sel4[1] sel4[0] Out4(1:0) w(1:0) w[1] w[0] In4(3:0) sel4(1:0) VERILOG OVERVIEW12/20/2015 15

- 16. Primitives No declaration required (predefined) Can only be instantiated Example: and a1 (C, A, B); //instance name • Usually better to provide instance name for debugging. Example: or o1 (SET, ~A, C ), o2(N, ABC,SET ); Example: and #(10) a2(o, i1, i2); // name + delay VERILOG OVERVIEW12/20/2015 16

- 17. 12/20/2015 VERILOG OVERVIEW 17 Test Bench module <test module name> ; // Data type declaration // Instantiate module ( call the module that is going to be tested) // Apply the stimulus // Display results endmodule Usefull commands: • initial • #delay • forever Tester DUT (Design Under Test) Test bench

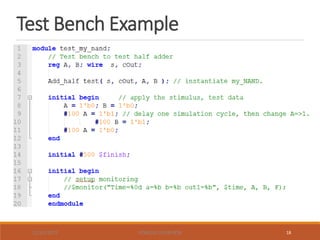

- 18. 12/20/2015 VERILOG OVERVIEW 18 Test Bench Example

- 20. Overview Simulation tools: • Aldec Active-HDL • Xilinx Isim • Modelsim • Altium Designer • … Simulation Phases: • Pre-synthesize (our talk) • Post-synthesize • Post-Place and root VERILOG OVERVIEW12/20/2015 20

- 21. Active HDL Tutorial Creating a simple project in Active HDL Step 1: Create a new workspace VERILOG OVERVIEW12/20/2015 21

- 22. Active HDL Tutorial Step 2: name your workspace VERILOG OVERVIEW12/20/2015 22

- 23. Active HDL Tutorial Step 3: Choose “Create an Empty Design with Design Flow”. VERILOG OVERVIEW12/20/2015 23

- 24. Active HDL Tutorial Step 4: Set default language to VERILOG VERILOG OVERVIEW12/20/2015 24

- 25. Active HDL Tutorial Step 5: Enter a name for your design VERILOG OVERVIEW12/20/2015 25

- 26. Active HDL Tutorial Step 6: Make a new Verilog Source VERILOG OVERVIEW12/20/2015 26

- 27. Active HDL Tutorial Step 7: follow the wizard VERILOG OVERVIEW12/20/2015 27

- 28. Active HDL Tutorial Step 8: Enter the name of your Verilog module VERILOG OVERVIEW12/20/2015 28

- 29. Step 9: Add ports to your module Active HDL Tutorial VERILOG OVERVIEW12/20/2015 29

- 30. Active HDL Tutorial Step 10: Add your code after port declaration (here the continuous assignment for adder) VERILOG OVERVIEW12/20/2015 30

- 31. Active HDL Tutorial Step 11: Compile the module VERILOG OVERVIEW12/20/2015 31

- 32. Active HDL Tutorial Step 12: Initialize Simulation VERILOG OVERVIEW12/20/2015 32

- 33. Active HDL Tutorial Step 13: the software will ask you to select the Top-level module… do it! VERILOG OVERVIEW12/20/2015 33

- 34. Active HDL Tutorial In case you get this error… VERILOG OVERVIEW12/20/2015 34

- 35. Active HDL Tutorial Go to Design > Setting > Simulation > Verilog and uncheck “Verilog Optimization” VERILOG OVERVIEW12/20/2015 35

- 36. Active HDL Tutorial Step 14: from File > New > Waveform open a new waveform window VERILOG OVERVIEW12/20/2015 36

- 37. Active HDL Tutorial Step 15: Select signals from the left window and Drag-and-Drop them to the right VERILOG OVERVIEW12/20/2015 37

- 38. Active HDL Tutorial Step 16: Right click on any signal in the right panel and select Stimulators (if it is already inactive, make sure initialization is performed) VERILOG OVERVIEW12/20/2015 38

- 39. Active HDL Tutorial Step 17: choose stimulator for input signala VERILOG OVERVIEW12/20/2015 39

- 40. Active HDL Tutorial Step 18: now you can run simulation by pressing “run for” button. VERILOG OVERVIEW12/20/2015 40

- 41. 12/20/2015 VERILOG OVERVIEW 41 For more tutorials please visit our website Click Here

![Interconnecting Modules

In order to use a module, it should be

instantiated:

<Module_name> <Instant_name> (<port mapping>)

Example: using two mux2 to build a mux4

(actually this is not an mux4-1 !!!)

In(1 :0 ) O ut

se l

mux2_i1

mux2In4(3:0)

sel4(1:0)

In(1 :0 ) O ut

se l

mux2_i2

mux2

In4(3:2)

In4(1:0)

sel4[1]

sel4[0]

Out4(1:0)

w(1:0)

w[1]

w[0]

In4(3:0)

sel4(1:0)

VERILOG OVERVIEW12/20/2015 15](https://image.slidesharecdn.com/verilogoverview-151220130653/85/Verilog-overview-15-320.jpg)